# HIGH PERFORMANCE FPGA Implementation of RS Codec for DVB

Ram Krishna Sharma, EC ,RGPV , ggits, Jabalpur, mp ,india <u>ram.mtech87@yahoo.com</u> pn 7354085395

#### ABSTRACT

Reed Solomon Forward Error Correction (FEC) Codes plays an important role in digital communication and storage systems to increase the transmission reliability and to achieve better error correction performance. RS codes are applied in many systems and adopted by various standards such as storage devices, mobile communications, high-speed modems, DVB T, DVB S, DVB DSNG, DVB C, IEEE 802.16, OTN G.709, etc. In this paper, design and FPGA implementation of RS (204, 188) encoder and decoder is presented for DVB application. This paper proposed a performance analysis and efficient design methodology for serial concatenation coding for DVB system and its implementation on the Virtex 4 xc4vlx15-12-sf363 FPGA chip. The area occupied and speeds at which the proposed design can run are two performance metrics used for performance analysis.

#### INTRODUCTION

In recent years, the tremendous growth in mobile and multimedia communications has produced a corresponding increase of demand and efforts in the development of highly efficient data transmission codes. The received data is very much error prone in wireless channel, which require them to be protected prior transmission. One of the popular techniques used is Forward Error Correction (FEC) scheme that employs a certain error correction codes [1]. Therefore, Error Control Coding (ECC) is done to prevent the output of erroneous bits despite noise and other imperfections in the channel in which extra bits are added to the data at the transmitter (redundancy) to permit error detection or correction at the receiver.

Error detection and retransmission and Forward Error Correction (FEC) are two techniques to correct the transmission errors. Error detection in a block of data can then request a retransmission, known as Automatic Repeat Request (ARQ) for sensitive data. It is appropriate for Low delay channels and Channels with a return path and not appropriate for delay sensitive data, e.g. real time speech and data. Forward Error Correction (FEC) coding is designed so that errors can be corrected at the receiver. This is appropriate for delay sensitive and oneway transmission (e.g., broadcast TV) of data. Block codes and Convolution Codes are two types of FEC Codes. Reed-Solomon (RS) codes are popular FEC scheme discovered and described in a paper by Reed and Solomon in 1960 [2]. RS codes are very effective in correcting random symbol errors and random burst errors. RS Codes are Reed-Solomon codes are block-based error correcting codes and applied in wide range of systems including storage devices such as, Compact disc DVD, wireless and mobile Communications e.g. microwave links, cellular telephones, Digital satellite Communications and Digital television/Digital Video broadcasting (DVB) [3] and highspeed modems, power line Communication and High speed modem such as ADSL etc.

The encoder attaches parity symbols to the data before transmission using a predetermined algorithm before transmission. At the receiving side, the decoder detects and corrects a limited predetermined number of errors occurred during transmission. Transmitting the extra parity symbols requires extra bandwidth compared to transmitting the original data but transmitting additional symbols introduced by FEC is better than retransmitting the whole package when at least an error has been detected by the receiver. Implementing Reed- Solomon codec on reconfigurable devices is becoming more attractive because FPGAs provide flexibility where the algorithm parameters can be altered to provide different error correction capabilities. Also they provide a rapid development cycle, resulting in a short time to market.

1

#### **DIGITAL VIDEO BROADCASTING**

The *Digital Video Broadcasting (DVB)* Project is an alliance and industry-led consortium of over 260 broadcasters, manufacturers, network operators; Regulatory bodies committed to designing technical specifications for the global delivery of digital television and data services [4]. DVB has three standards that use identical RS code parameters. These are satellite (DVBS), cable (DVB-C) and terrestrial (DVB-T).All DVB standards employ the same (204,188) RS code and operate in GF

#### © 2013 IJAIR. ALL RIGHTS RESERVED

(28). Therefore, the same Galois Field arithmetic units and hardware can be used for different DVB standards. Table I summarize RS parameters for DVB standard.

#### Table I : RS Code Specification for DVB Standard

| Symbol width (Bits/Symbol)     | m     | 8                                                  |                                                               |

|--------------------------------|-------|----------------------------------------------------|---------------------------------------------------------------|

| Field Generator polynomial     | P(x)= | = x <sup>8</sup> +x <sup>4</sup> +x <sup>3</sup> + | z <sup>2</sup> +1                                             |

| Code Generator polynomial      | g(x)= | =( x-a <sup>0</sup> )( x-                          | α <sup>1</sup> ) (x · α <sup>2</sup> ) (x · α <sup>15</sup> ) |

| Symbol per block (code length) | n     | 204                                                | Range 4:255                                                   |

| Data symbols (message length)  | k     | 188                                                | Range<br>76:202                                               |

#### **REED SOLOMON CODEC**

#### **Reed-Solomon Codes Overview**

Channel coding systems based on Forward Error Correction (FEC) systems, play a crucial role in today's digital transmission and storage systems. Reed-Solomon (RS) codes are a prominent representative of FEC block codes that allow recovering as many lost packets (erasures) as the number of parity packets transmitted. They were discovered in 1960 by

2

Reed and Solomon and can be considered as a special case of a larger class of FEC block codes called BCH (Bose-Chaudhuri-Hochquenghem) codes. RS codes are based and operate on a special area of mathematics known as Galois fields or finite fields. A finite field has the property that arithmetic operations  $(+, -, \times, /, \text{ etc})$  on field elements always have a result in that field. The elements of the Galois field are often referred to as the RS symbols .A RS encoder or decoder needs to carry out these arithmetic operations. All valid codeword are exactly divisible by the generator polynomial which generate RS codeword. The general form of the generator polynomial is given as [1]:

The General form of polynomial is given as :

$$G(\mathbf{x}) = (\mathbf{x} \cdot \alpha^{1})(\mathbf{x} \cdot \alpha^{1}) \dots (\mathbf{x} \cdot \alpha^{1+2})$$

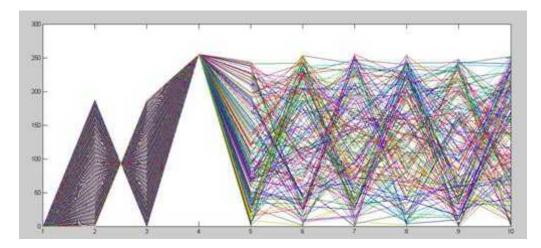

Codeword is constructed using [2]

$$C(\mathbf{x}) = G(\mathbf{x}). I(\mathbf{x})$$

[2]

Where G(x) is a generator polynomial, I (x) is the information blocks, C(x) is valid codeword and is referred as primitive element of the field.

The block length determines which field the code is defined over. In particular, if m is the number of bits employed to represent each symbol, the block length n is equal to  $2_{m}$ - 1. The most commonly used RS code operates on GF (256) with symbols of eight bits (one byte), such that there is a direct translation between bytes and RS symbols. Systematic Reed Solomon codes are referred to as RS (n, k, 2t) code, where the first k (k < n) symbols are the source symbols which are to be protected, and the remaining (n -k) symbols are the parity (repair) symbols which are calculated based on the source data. k/n is the code rate. Reed-Solomon codes can correct as many lost symbols than the number of parity symbols transmitted if reliable erasure information is provided. On the other hand, when there are too many errors/erasures, the RS decoder will not be able to correct anything, and just provide output as source symbols without error correction. A RS code operating on symbols of eight bits allows code parameters of any k < 255, and any n, with k <n 255.

# **Concatenated FEC Codes For Improved Performance**

© 2013 IJAIR. ALL RIGHTS RESERVED

It is known that the concatenated coding scheme using inner code and outer code can achieve good BER performance. In satellite communication systems, the concatenated coding scheme using the convolutional coding with Viterbi decoding for the inner code and the Reed Solomon (RS) code for the outer code is used. In the concatenated coding scheme, the interleaving and de interleaving are required between the inner code and outer code because the burst errors occur in the output of convolutional decoder in the receiver.

3

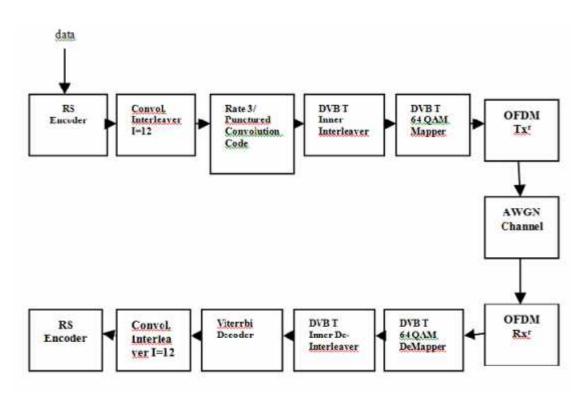

This paper focuses only on forward error correction (FEC) Coder and decoder and its implementation. In this paper, transmission system that we use is composed of serial concatenation of the Reed-Solomon RS (204,188) shortened) code and rate <sup>3</sup>/<sub>4</sub> punctured convolutional code with 64 QAM [5]. Convolutional FEC codes are very popular because of their powerful error correction capability and are especially suited for correcting random errors.

# PROPOSED CONCATENATED FEC CODEC DESIGN

#### **Matlab Based Design and Simulation**

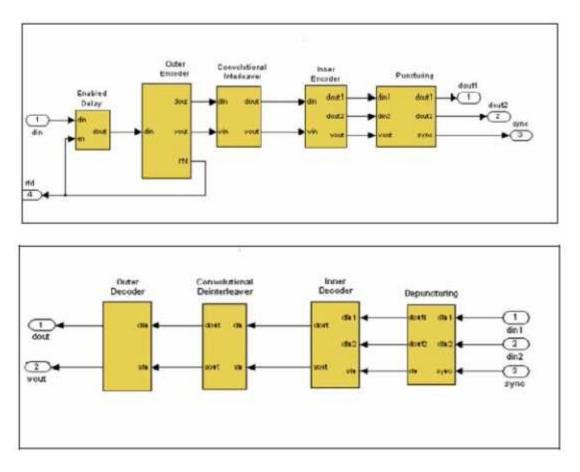

The proposed FEC codec for DVB standard has been designed and simulated using Matlab 2007a. The proposed design models the transmitter in its 2k mode, as prescribed in the standard, model one possible receiver design and generate error statistics that will help in determining whether the receiver model satisfies the performance requirements. Proposed model includes the major functional blocks as shown in table II. Fig 1 shows the concatenation of convolutional code as inner code and Reed Solomon code as outer codes.

| Outer Coder              | (204,188) Shortened RS Encoder    |

|--------------------------|-----------------------------------|

| Inner coder              | Rate ¾ punctured Convolution code |

| Outer Interleaver        | Convolution Interleaver I=12      |

| Inner Interleaver        | DVB Inner Inerleaver              |

| Mapper and Demapper      | DVB 64 QAM Mapper and Demapper    |

| Transmitter and Receiver | OFDM Transmitter and Receiver     |

| Channel                  | AWGN channel                      |

#### Fig 1 : DVB channel Transmitter and Receiver

Proposed FEC Codec also includes a source of random data, a channel model, error statistic calculators, and several sinks as shown in figure 2. Soft decisions are computed using an A64-QAM demapper that makes soft decisions, producing a set of six real numbers for each complex number in its input. These six numbers represent soft decisions on the real and imaginary components first bit, second bit, and third bit. The Viterbi Decoder subsystem interprets the soft-decision numbers and uses them to decode the punctured convolutional code properly.

In-phase and quadrature phase signal components are extracted after appropriately scaling the received signal, and then they are shifted to obtain soft decisions for various bits. Rectangular QAM Demodulator block can be configured to compute exact bitwise log-likelihood ratios (LLRs). Noise variance needs to be provided and it is computed using the received signal and the signal generated by the DVB 64-QAM Mapper. This technique makes derivation of soft decisions easy for any signal constellation. Block Diagram of Matlab Simulation model of Concatenated DVB channel coding is shown in Fig 2.

5

Fig 2 : Block Diagram of Matlab Simulation Model

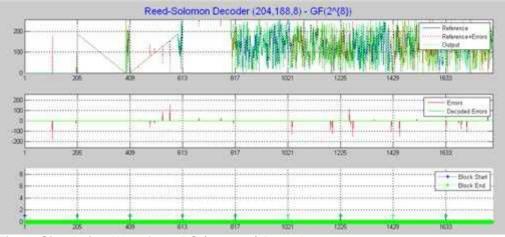

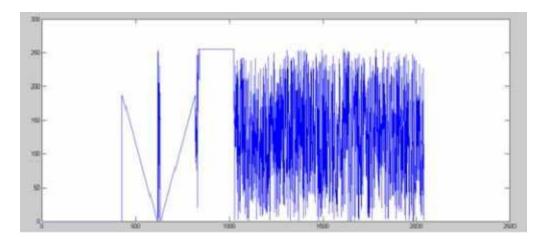

Reed-Solomon codes (RS codes) are non-binary BCH codes. The error-correcting capability of RS codes is more powerful combined with data interleaving technique. Unscramler is added to front end of decoder and Interleaver is added to Back- End of encoder. An interleaver can be used to spread the Viterbi output error bursts across multiple R-S codewords for burst error correction. Thus burst error of memory systems are scatter and burst error becomes random error .Based on above designs of codec and Interleaver, error-correcting ability is simulated by Matlab for RS (204,188) code. Simulation waveforms of RS decoding for DVB standard is shown as Fig.3.

Fig 3 : Simulation Waveform RS (204,188) Decoder

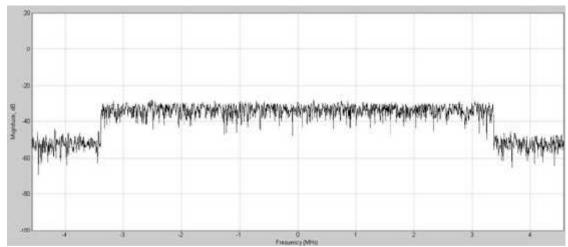

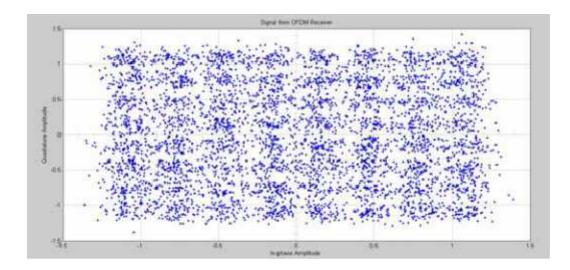

Spectrum scope display that shows the received signal spectrum and Scatter plot display that shows the received signal constellation are given by figure 4 and 5 respectively.

Fig 4 : Received Signal Spectrum Output

Fig. 5 : Received Signal Constellation Output

# FPGA IMPLEMENTATION OF RS CODEC

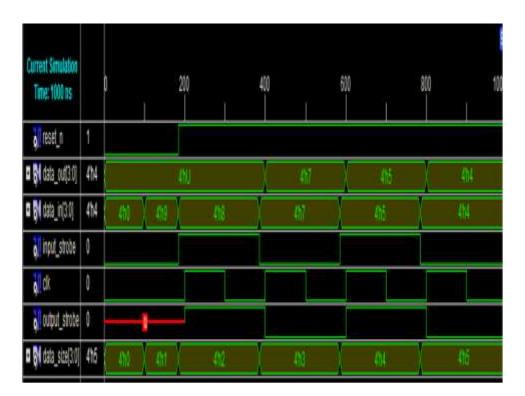

The Reed-Solomon (255,239) was implemented using VHDL hardware description language, which offers high abstraction level during the implementation. The VHDL description was simulated and implemented in a Xilinx ISE 9.2i Virtex 4 **xc4vlx15-12-sf363** FPGA.

Fig. 7 : RS Coded Data

Fig. 8 : Showing All Corrected Errors and Erasures after Decoding

## The FPGA Realization of FEC Codec

**1. Encoder** : The data is systematically coded. It is first sent the original data, followed by the parity symbols, which are calculated according to the polynomial generator. It is used a "2t step" polynomial generator, given by expression.

$$g(X) = \prod_{i=1}^{b+2t-1} (x + a^{i})$$

[3]

where b is a random number. It must be carefully chosen to avoid increasing the system complexity. The DVB standard takes b as 0. Encoder includes feedback shift register, finite field adders, finite field multipliers, switches. Computing unit is mainly finite field multipliers and finite field adders. Because the domain is characterized by 2, so finite field adders and multipliers are implemented by exclusive-OR logic, and switches are implemented by AND logic.

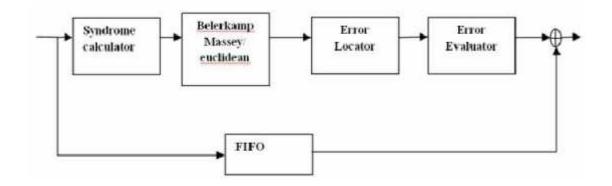

2 **Decoder :** The decoder is comprised of five blocks: Syndrome Calculator, Key Equation Solver, Error Locator, FIFO and Error Evaluator, as indicated in Figure 9.

#### Fig. 9 : Block Diagram of Implemented RS Decoder

The Syndrome Calculator is the first block which monitors the arriving data to evaluate if data correction processing is necessary. It verifies if an error occurred du during the transmission by obtaining all the polynomial roots throughout the data. If the number of errors is smaller than or equal to t, then the syndrome is delivered to the Key Equation Solver block. If the number of errors is larger than t, an error signal is generated to indicate that no correction is possible. Finally, if no errors are found, the data is delivered without any further processing, besides removing the parity symbols.

9

The Euclidian and the Berlekamp-Massey algorithm are two possible algorithm options for the Key Equation Solver. Error Locater finds the error locations using the Chien Search algorithm. The error magnitude to be added to those locations in order to correct the symbol is also determined by this [7].

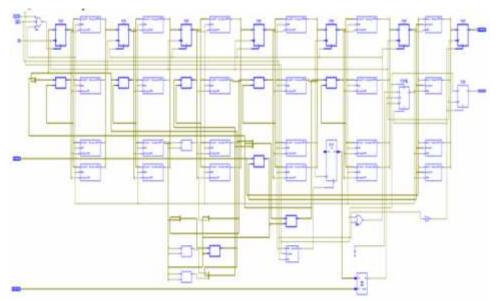

In this paper, the design has been accomplished RTL description using VHDL and continues with the synthesis using Xilinx Virtex 4 **xc4vlx15-12-sf363** FPGA using ISE Synthesis tool. Both encoder and decoder are synthesized targeting **xc4vlx15-12-sf363**. The synthesis report of the RS Encoder and RS Decoder when using Virtex 4 **xc4vlx15-12-sf363** as target device is summarized in table III.

| Device Utilization Summary                     |      |           |             |         |  |  |

|------------------------------------------------|------|-----------|-------------|---------|--|--|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |  |  |

| Number of Sice Rip Rops                        | 30   | 12,288    | 13          |         |  |  |

| Number of 4 input LUTs                         | 58   | 12,288    | 15          |         |  |  |

| Logic Distribution                             | (    |           |             |         |  |  |

| Number of occupied Sices                       | 31   | 6,144     | 1%          |         |  |  |

| Number of Slices containing only related logic | 31   | 31        | 100%        |         |  |  |

| Number of Slices containing unrelated logic    | 0    | 31        | 0%          |         |  |  |

| Total Number of 4 input LUTs                   | 58   | 12,288    | 15          |         |  |  |

| Number of bonded OBs                           | 16   | 240       | 6%          |         |  |  |

| Number of BUFG/BUFGCTRLs                       | 1    | 32        | 3%          |         |  |  |

| Number used as BUFGs                           | 1    |           |             |         |  |  |

| Number used as BUFGCTRLs                       | 0    |           |             |         |  |  |

| Total equivalent gate count for design         | 628  |           |             |         |  |  |

| Additional JTAG gate count for IOBs            | 768  |           |             |         |  |  |

DEVICE UTILIZATION SUMMARY

RTL VIEW

10

WAVEFORM

#### **Contrast With Other Design**

We compare our design with other existing codec solutions[5] for RS Encoder and Decoder as listed in Table III. We can see from this comparison table that the LEs count of our design is the least. That means the RS Codec in this paper has reduced hardware complexity. The design in [5] is a RS codec which used parameterization approach for both DVB and 802.16 networks.

# Table III : The Comparison Table of Hardware and Timing Performance of RS $\operatorname{Encoder}$

|                                   | RS ENCODER (5)   | PROPOSED RS ENCODER |

|-----------------------------------|------------------|---------------------|

| <b>Device Utilization Summary</b> |                  |                     |

| Number of Slices                  | 95 out of 6144   | 31 out of 6144      |

| No. of slice flip flops           | 156 out of 12288 | 30 out of 12288     |

| No. of 4 input LUTs               | 168 out of 12288 | 58 out of 12288     |

| No . of bonded IOBs               | 16 out of 240    | 16 out of 240       |

| Timing summary                    |                  |                     |

| Speed grade                       | -12              | -12                 |

| Minimum Period                    | 3.676 ns         | 3.2420 ns           |

| Maximum frequency                 | 272.045 MHz      | 308.5 MHz           |

11

# CONCLUSION

In this paper, Concatenated FEC Codec has been presented to remove error in wireless communication particularly for DVB-T application. The FEC Codec design is done by concatenating RS (Reed Solomon) and Convolution codes. The analysis and simulation is done using Matlab 2007a. We implemented a concatenated coding system based on (204, 188) RS code via a very high-speed hardware description language (VHDL) and synthesized for the FPGA chip Vertex IV xc4vlx15-12-sf363. The result shows that the coder could operate at a max frequency of 308.5 MHz. This design is also suitable for systems such as cable modem and other digital video broadcasting (DVB) standards such as DVB C, DVB S. The proposed Reed Solomon codec has

higher maximum frequency as well as occupies less area of FPGA in comparison to RS Codec proposed in [5] design.

#### **FUTURE SCOPE**

Coding field of communication is highly growing area in present era of research. Still, it needs a lot of improvement in the field of error correction and coding techniques. By improving concatenation technique i.e. by concatenation of LDPC (Low Density Parity Check) as inner code and RS (Reed Solomon) as outer coding, we can enhance the performance of FEC system for DVB application. The goal of our present work is to reduce the occupied area of FPGA and increase the efficiency. The development of highly effective decoding algorithms for the implementation is another area where the significant amount of research work can be done and RS code can be made more suitable for different standards for DVB i.e. DVB S2, DVB C, etc.

#### REFERENCES

[1] Lin, S. and D. J. Costello. 1983. Error Control Coding: Fundamental and Application. Pearson Prentice Hall.

[2] I. S. Reed and G. Solomon, "Polynomial Codes over Certain Finite Fields", Journal of the Society of Industrial and Applied Mathematics. Pp 8: 300–304, 1960

[3] Wicker, S. B. and E. Bhargava. 1994. Reed-Solomon Codes and their Applications. New York: IEEE Press.

[4] DVB, "Framing Structure, channel coding and modulation for digital terrestrial television", ETSI EN 300 744, Vol 4.1, January 2001

[5] Bhawana Tiwari and Rajesh Mehra "FPGA Implementation of RS Codec for Digital Video Broadcasting" VSRD-IJEECE, Vol. 2 (2), 2012, 68-77.

[6] Lamia Chaari, Mohamed Fourati, Nouri Masmoudi, Lotfi Kamoun, "A reconfigurable FEC system based on Reed Solomon Codec for DVB and 802.16 network", WSEAS Transactions on Circuits and Systems, Issue 8,, volume 8, pp 729-744, August 2009.

[7] K. C. C. Wai and S. J. Yang, Field Programmable Gate Array Implementation of Reed-Solomon Code, RS(255,239), New York (2006).

[8] T. Le-Ngoct, M. T. Vot, B. Mallettt and V. K. hargava, in Military Communications Conference, 1990. MILCOM '90, Conference Record, A New Era/1990, p. 121-125, A Gate-array-based programmable Reed- Solomon codec : structure-implementation-applications, Monterey, CA (1990).

[9] Liyi Xiao, Zheng Sun, Ming Zhu, "Efficient encoding and decoding algorithm used in Reed-Solomon codes for multiple fault-tolerance memories", 2011 Cross Strait Quad-Regional Radio Science and Wireless Technology Conference, pp.1569-1572, July 26-30, 2011

[10] Jiabin You, Shaochuan Wu, "Design and Realization of Reed-Solomon Codec Based on FPGA Technique", 2011 International Conference on Mechatronic Science, Electric Engineering and Computer, pp. 2086- 2089, August 19-22, 2011

[11] Chang Limin, Song Lu, Duan Fengyang "Research and Realization of RS Codec based on FPGA Technique", proceeding of International Conference on Mechatronics and Automation, Changchun, China, pp. 481-486, 9-12 August 2009.

[12] Emanuel Marconetti, Romain Gudnard, Damian Savage, Pat Crowe, Iiiigo Epelde, Louise Bradley Flavio Cali, "A Fully Programmable Reed Solomon 8-Bit Codec Based on a Re Shaped Berlekamp Massey Algorithm", IEEE International Symposium on Circuits & Systems (ISCAS '02), Vol 5, pp. 553–556, 2002.

[13] Hanho Lee. "An Ultra High-Speed Reed-Solomon Decoder", IEEE International Symposium on Circuits & Systems (ISCAS'05), Vol. 2, pp. 1036-1039, 2005.

[14] Gabriel Marchesan Almeida, Eduardo Augusto Bezerra, Luis Vitório Cargnini Rubem Dutra Ribeiro Fagundes Daniel Gomes Mesquita "A Reed-Solomon Algorithm for FPGA Area Optimization in Space Applications", NASA/ESA Conference on Adaptive Hardware and Systems, pp. 243-249, 2007.

[15] Teodor Iliev, Izabella Lokshina, Dimitar Radev, Georgi History, "Analysis and Evaluation of Reed– Solomon Codes in Digital Video Broadcasting Systems", IEEE Symposium on Wireless Telecommunication (WTS'08), pp. 92-96, 2008.