# Design and Implementation of Speed Efficient MAC Unit Based on Ancient Vedic Multiplication Technique

Mr. Yogesh Kumar[1], Mr. Kanak Kumar[2], Mr. Santosh Yadav[3] Department of Electronics & Communication M.tech-IVth semester[1], Assit. Professor[2,3]

Millennium Institute of Technology[1,2,3] Rajeev Gandhi Technical University, Bhopal, Madhya Pradesh, India[1,2,3]

> <u>yogeshkumarg3891@gmail.com</u> <u>kanakkumar.iitkgp@gmail.com</u>

Abstract— This research work is devoted to design high speed thirty two bit Multiply Accumulate Unit. MAC Unit is the key element of digital signal processors to perform various sophisticated tasks like as FFT, DFT, resolving various complex equations and Convolution etc. along with this it is also used in various configurations like as IIR, FIR etc. Every digital domain based technology depends upon the operations performed by MAC Unit either partially or whole. Speed is the most prominent factor of processor and controllers being used recently. That's why it is highly required to design high speed MAC, which can enhance the efficiency of those modules which lies upon the operations performed by MAC. The speed of MAC greatly depends upon the speed of multiplier. At algorithmic and structural level there are so many multiplication algorithms exist now-a-days. After a thorough study and proper analysis we have seen that Vedic multiplication technique is the best algorithm that gives much better result in comparison to others in terms of speed. Further we have analyzed different existing Vedic multiplication hardware, and compared those with respect to speed. And found that the Vedic multiplier with Carry Save Adder gives better outcome. Then we have proposed that multiplier for the MAC unit design. This proposed MAC Unit is able to perform different arithmetic operations at high speed. All sub-modules in the MAC unit has been designed in combinatorial form. And integrated in the final module, in which we have provided the reset and clock functionality to have better control on the circuitry. To design proposed multiply accumulate unit verilog hardware description language (HDL) has been used. To design operational sub-modules data flow modeling and to integrate these modules behavioral modeling style has been used. For this design the target FPGA belongs to Spartan-3E (family), XC3S500E (device), FG320 (package) with speed grade of -5. For synthesis purpose Xilinx synthesis tool (XST) of Xilinx ISE-9.2i has been used. For the behavioral simulation purpose ISE simulator has been used.

Keywords-MAC, Vedic Multiplier with CSA, Xilinx-ISE9.2i,

#### I. INTRODUCTION

Today in the digital domain world digital signal processing is of main concern, whose performance is mainly dependent upon the MAC unit. MAC unit optimization can also provide the Digital Signal Processors' performance optimization, and Multiplication is the main operation in MAC unit. Multiplication is the most time consuming module amongst the basic mathematical calculation. With these considerations, it is always important to have fast and efficient mechanism to implement mathematical functions. Vedic Mathematics is a name which is heard many times by us from childhood to solve complex mathematics problem mentally. One of the main purposes of Vedic mathematics is to transform the tedious calculations into simpler, orally manageable operation without much help of pen and paper. Any ordinary human can perform mental operations for very small magnitude of numbers and hence Vedic mathematics provides techniques to solve operations with large magnitude of numbers easily by converting it to small magnitude of numbers. Vedic mathematics provides more than one method for multiplication operations. For each operation there is at least one generic method provided along with some methods which are directed towards specific cases simplifying the calculations further. [2] has described the Vedic mathematics thoroughly. Vedic mathematics provides algorithms to simplify the mathematics and hence is perfect solution for the problem stated. After a thorough and comparative study we have found that Vedic multiplier designed by [1] is better than other available multipliers.

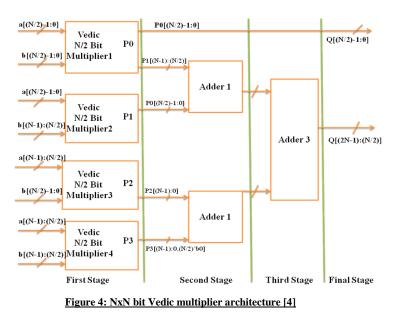

Before designing our proposed MAC unit it's imperative to elaborate the working of the Vedic multiplier:-

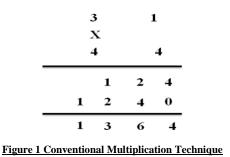

In our daily life all of us, perform so many tasks based upon simple calculations, which is based upon conventional multiplication algorithm of the arithmetic. So it can be easily said that all of us are very familiar with conventional multiplication algorithm. It is very tedious to multiply two numbers with large in magnitude than with smaller in magnitude, as human mind is not able and not trained to handle these large magnitude numbers. It can be illustrated using a very simple example, where we have taken the multiplier and multiplicand of two digit length. Suppose we want to multiply 31 with 44:-

To perform conventional multiplication: -

Multiply 31 with first RHS digit 4 = 124. And store it in register.

Then multiply second RHS digit 4 with 31 = 124.

Provide left padding of 1 digit = 1240.

Add first partial product with second. And get result, which is 1364.

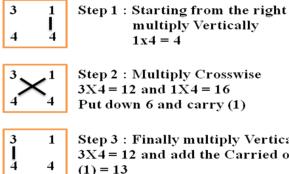

This is a very handy job. So, to handle these kind of problems mental mathematics (Vedic mathematics), developed by the Jagatguru Swami Balkrishna Teerth Ji Maharaj based approaches can be used, to have a better outcome. This is based upon sixteen formulas and sixteen sub-formulas. Using mental multiplication approaches, suggested by Vedic mathematics, Human mind can be trained to perform the multiplication of numbers with the large magnitudes also. Actually the logic behind this one is that, the Vedic (mental) multiplication breaks the multiplication of large magnitude numbers into the multiplication of small magnitude numbers. There are two algorithms which are suggested by the Vedic mathematics, first one is the Urdhva Triyambakam and second one is the Nikhilam. But Nikhilam algorithm doesn't provide better outcome in all cases, it provide better result only then when multiplier and multiplicand both are near to the base, for other cases it has some limitations. So, it can't be used universally. Vedic Urdhva Triyambakam algorithm is the multiplication algorithm, which provide better outcome in all cases, and so can be applied to all type of numbers universally. This is illustrated using an example where multiplier and multiplicand of two digit length. Suppose we want to multiply 31 with 44 using the Vedic (mental) multiplication approach:-

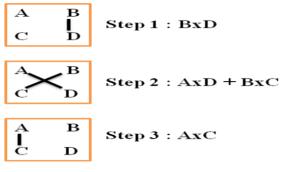

First we are showing the syntax for two digit multiplication using Vedic multiplication approach:-

Figure 2 two bit vedic multiplication syntax

Then with the use of above given syntax the multiplication has been performed, which is shown below:-

Step 3 : Finally multiply Vertically 3X4 = 12 and add the Carried over

On the basis of above example we can say that how efficient the Vedic multiplication is.

After a thorough study we have found that [1] has introduced a new approach to design the architecture of Vedic multiplier, Apart from vedic multiplier there are two popular methods to perform multiplication operation first one is Wallace due to its high speed because of its unique addition tree structure and second one is Booth that takes less area to perform multiplication. Using combination of these two techniques a high speed multiplier has been designed known as Modified Booth Wallace Multiplier. We also have proposed the combination of Urdhva Triyakbhyam sutra with unique addition tree structure similar to Wallace for multiplication to design MAC unit. Here [1] has used conventional Vedic multiplier for design of 2x2 bit multiplier and for higher level multiplier [1] has replaced the Conventional Adder which is required during the Partial Product generation with unique addition tree structure similar to Wallace addition tree structure and found that our proposed design is better than conventional Vedic multiplication hardware in terms of speed.

#### II. PROPOSED MAC UNIT

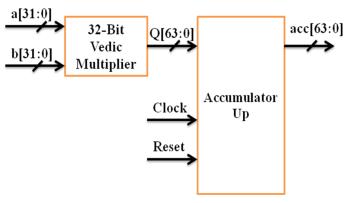

The proposed 32-bit MAC unit's block diagram can be shown as below: -

Figure 4 Proposed MAC unit Block Diagram

Here multiplier and multiplicand are the two 32-bit inputs of our MAC Unit. And other sections of the design are selfexplanatory. We have compared various Multipliers and found that Vedic Urdhva Triyambakam is the better multiplier in comparison to other conventional Multipliers. Now here a basic question arises that why we have not used Multiplier of XILINX CORE IP, the answer is simple is if we put clock in that XILINX CORE IP multiplier then its SET-UP and HOLD-TIME gets increased in comparison to our proposed Vedic Multiplier.

### III. COMPARATIVE RESULTS OF PROPOSED VEDIC MULTIPLIER FOR MAC UNIT

To show the efficiency of proposed Vedic multiplier, it has been implemented and compared with other popular multiplier structures based on different multiplication algorithms on the same platform of target FPGA, which has been used to implement these popular multiplier structures. We have compared our module with different modules and shown comparison on the basis of provided results availability of results. Comparison tables are shown below:-

• In the following given table, target FPGA belongs to Spartan 3AN (family), XC3S50A (device), -7 (speed grade). this multiplier is with clock circuitry, so we have also placed clock circuitry with our multiplier: -

| Path Delay (in ns) for different multipliers at sixteen bit level |          |  |

|-------------------------------------------------------------------|----------|--|

| Urdhva Triyagbhyam<br>multiplier [31]                             | Proposed |  |

| 21.647                                                            | 6.463    |  |

• In the following given table which target FPGA has been used belongs to Spartan 3 (family), XC3S400 (device), TQ144 (Package), -5 (speed grade).

| different multipliers at eight bit level |                             |                                         |                                         |          |  |

|------------------------------------------|-----------------------------|-----------------------------------------|-----------------------------------------|----------|--|

| Array<br>Multiplier<br>[33]              | Booth<br>Multiplier<br>[33] | Vedic<br>Multiplier<br>with KSA<br>[33] | Vedic<br>Multiplier<br>with KSA<br>[32] | Proposed |  |

| 32.01                                    | 29.549                      | 23.644                                  | 28.699                                  | 19.467   |  |

Maximum Combinational Path Delay (in ns) for

In the following given table which target FPGA has been used belongs to Spartan 3E (family), XC3S500E (device), FG320 (Package), -5 (speed grade).

|    | Multiplier<br>[34] | multiplier<br>with CSA<br>[34] |        |

|----|--------------------|--------------------------------|--------|

| 8  | 31.029             | 15.418                         | 15.673 |

| 16 | 46.811             | 22.604                         | 20.337 |

• In the following given table which target FPGA has been used belongs to Virtex-5 (family), XCVLX50 (device), FF324 (Package), -2 (speed grade).

(in

MHz)

for

Frequency

Maximum

different

| Bit level | Normal<br>Booth<br>Multiplier<br>[35] | Urdhva<br>multiplier<br>[35] | Proposed |

|-----------|---------------------------------------|------------------------------|----------|

| 16        | 100                                   | 233.3                        | 316.636  |

In the following given table which target FPGA has been used belongs to Spartan3 (family), XC3S50 (device), PQ208 (Package), -5 (speed grade).

Maximum Combinational Path Delay (in ns) for

| Bit level | Urdhva     | Urdhva     | Proposed |

|-----------|------------|------------|----------|

|           | Multiplier | Multiplier |          |

|           | with RCA   | with CLA   |          |

|           | [36]       | adder [36] |          |

| 1         | 17.796     | 17.560     | 15.673   |

In the following given table which target FPGA has been used belongs to Spartan3E (family), XC3S500E (device), FG320 (Package), -5 (speed grade).

Maximum Combinational Path Delay (in ns) for different multipliers at four bit level

| Arrav  | KCM | Urdhva | Proposed |

|--------|-----|--------|----------|

| 1111uj | nom | crunvu | Toposed  |

|        |     |        |          |

| Multiplier<br>[37] | (Constant<br>coefficient<br>multiplier | multiplier<br>[37] |              | Maximum Combinational Path D<br>thirty two bit level | Delay (in ns) for MAC Unit at |

|--------------------|----------------------------------------|--------------------|--------------|------------------------------------------------------|-------------------------------|

|                    | [37]                                   |                    |              | MAC using Vedic<br>multiplier [45]                   | Proposed                      |

| 4                  | 18.792                                 | 22.864             | 13.954       |                                                      |                               |

|                    |                                        |                    |              | 14.69                                                | 6.100                         |

| In the follow      | ing given table                        | which target F     | PGA has been |                                                      |                               |

|                    | 00                                     | (family), XC3      |              | • In the following given                             | table which target FPGA has   |

used belongs to Spartan3 (family), XC3S50 (device), PQ208 (Package), -4 (speed grade).

| Maximum     | Combination       | Path     | Delay | (in | ns) | for |

|-------------|-------------------|----------|-------|-----|-----|-----|

| different m | ultipliers at fou | r bit le | vel   |     |     |     |

| -               |                  |          | thirty two bit level               |          |

|-----------------|------------------|----------|------------------------------------|----------|

| Array           | Vedic multiplier | Proposed |                                    |          |

| multiplier [38] | [38]             |          | MAC using Vedic<br>multiplier [45] | Proposed |

| 20.471          | 17.768           | 16.143   |                                    |          |

|                 |                  |          | 14.69                              | 6.100    |

• In the following given table which target FPGA has been used belongs to Virtex 2P (family), XC2VP2 (device), FG 256 (Package), -7 (speed grade).

| Maximum Combinational Path Delay (in ns) for different multipliers at eight bit level |                            |                                       |                                    |                               |                              |          |

|---------------------------------------------------------------------------------------|----------------------------|---------------------------------------|------------------------------------|-------------------------------|------------------------------|----------|

| Karatsuba<br>[41]                                                                     | Vedic<br>Karatsuba<br>[41] | Modified<br>Booth-<br>Wallace<br>[42] | Vedic with<br>Partitioning<br>[42] | Conventional<br>Vedic<br>[41] | Vedic<br>with<br>CSA<br>[39] | Proposed |

| 31.029                                                                                | 18.695                     | 15.815                                | 15.685                             | 15.418                        | 13.07                        | 11.886   |

• In the following given table which target FPGA has been used belongs to Spartan 3 (family), XC3S50 (device), PQ 208 (Package), -4 (speed grade).

Maximum Combinational Path Delay (in ns) for different multipliers at eight bit level

| Array [40] | Booth [40] | Conventional<br>Vedic [40] | Proposed |

|------------|------------|----------------------------|----------|

| 32.01      | 29.549     | 24.1                       | 19.467   |

• In the following given table which target FPGA has been used belongs to Spartan3E (family), XC3S500E (device), FG320 (Package), -5 (speed grade).

Maximum Combinational Path Delay (in ns) for MAC Unit at thirty two bit level

| MAC using<br>Wallace tree<br>[43] | MAC using Vedic<br>multiplier [43] | Proposed |

|-----------------------------------|------------------------------------|----------|

| 64.624                            | 37.799                             | 6.100    |

In the following given table which target FPGA has been used belongs to Spartan3E (family), XC3S100E (device), TQ144 (Package), -5 (speed grade).

## **IV. REFERENCES**

[1] Mr. Abhishek Gupta, Mr. Utsav Malviya, Prof. Vinod Kapse, "Design of Speed, Energy and Power Efficient Reversible Logic Based Vedic ALU for Digital Processors", 2012 NIRMA UNIVERSITY INTERNATIONAL CONFERENCE ON ENGINEERING, NUICONE-2012.

been used belongs to Spartan2 (family), XC2S200

(device), PQ208 (Package), -6 (speed grade).

Maximum Combinational Path Delay (in ns) for MAC Unit at

- [2] S G Dani, "Ancient Indian Mathematics A Conspectus\*", GENERAL\_ ARTICLE, RESONANCE, Springer Link, March 2012.

- [3] Pushpalata Verma, K.K. Metha, "Implementation of an Efficient Multiplier based on Vedic Mathematics Using EDA Tool", International journal of engineering and advance technology, ISSN: 2249-8958, June-2012, Volume-1, and Issue-5.

- [4] R.Bhaskar, Ganapathi Hegde, P.R.Vaya," An efficient hardware model for RSA Encryption system using Vedic mathematics". SciVerse Science Direct, ELSEVIER, Procedia Engineering Volume 30, 2012, Pages 124–128.

- [5] Devika Jaina, Kabiraj Sethi, Rutuparna Panda, "Vedic Mathematics Based Multiply Accumulate Unit", IEEE, 978-0-7695-4587-5/11, 2011.

- [6] S.S. Kerur, Prakash Narchi, Jayashree C N, Harish M. Kittur, Girish V A, "Implementation of Vedic Multiplier for Digital Signal Processing", proceedings published by International Journal of Computer Applications, presented in International conference on Vlsi, Communication and Instrumentation (ICVCI) 2011.

- [7] Balpande,S., Akare, U., Lande, S.," Performance Evaluation and Synthesis of Multiplier Used in FFT Operation Using Conventional and Vedic Algorithms", IEEE, 19-21 Nov.2010.

- [8] Syed Azman bin Syed Ismail\*, Pumadevi a/p Siva subramniam, "Multiplication with the Vedic Method", SciVerse Science Direct, ELSEVIER, Procedia Social and Behavioral Sciences 8 (2010), p.p.129–133.

- [9] Ashish Raman, Anvesh Kumar and R.K. Sarin, "Small area reconfigurable FFT design by Vedic Mathematics", , IEEE, 26-28 Feb. 2010.

- [10] Anvesh kumar, Ashish raman, "Low Power ALU Design by Ancient Mathematics", IEEE, 978-1-4244-5586-7/10, 2010.

- [11] Parth Mehta, Dhanashri Gawali, "Conventional versus Vedic Mathematical Method for Hardware Implementation of a Multiplier", IEEE, December 2009, p.p. 640-642.

- [12] M. Ramalatha, K. Deena Dayalan, P. Dharani, S. Deborah Priya, "High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques", IEEE, 978-1-4244-3834-1/09, 2009.

- [13] Ramesh Pushpangadan, Vineeth Sukumaran, Rino innocent, Dinesh sasikumar, Vaisak Sundar, "High Speed Vedic Multiplier for Digital Signal Processors", IETE Journal of Research, Volume 55, Issue 6, Nov-Dec 2009.

- [14] Harpreet Singh Dhillon and Abhijit Mitra, "A Reduced- Bit Multiplication Algorithm for Digital Arithmetics", International Journal of Computational and Mathematical Sciences 2:2, 2008 © www.waset.org Spring 2008.

- [15] Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim, Yong Beom Cho, "Multiplier Design Based On Ancient Vedic Mathematics", IEEE, 978-1-4244-2599-008, 2008.

- [16] Shamim Akhter, "VHDL Implementation of Fast NxN Multiplier Based on Vedic Mathematics", IEEE, Jaypee Institute of Information Technology University, Noida, 201307 UP, INDIA, 2007.

- [17] Himanshu Thapliyal, Saurabh Kotiyal and M. B Srinivas, "Design and Analysis of A Novel Parallel Square and Cube Architecture Based On Ancient Indian Vedic Mathematics", IEEE, Centre for VLSI and Embedded System Technologies, International Institute of Information Technology, Hyderabad, 500019, India, 2005.

- [18] HimanshuThapliyal and M.B Srinivas, "A High Speed and Efficient Method of Elliptic Curve Encryption Using Ancient Indian Vedic Mathematics", Proceedings of the 8<sup>th</sup> MAPLD Conference (NASA office of Logic Design), Washington D.C, USA, Sep 2005.

- [19] Purushottam D. Chidgupkar, Mangesh T. Karad, "The Implementation of Vedic Algorithms in Digital Signal Processing\*", Global J. of Engng. Educ., Vol.8, No.2 © 2004 UICEE Published in Australia 4th Global Congress on Engineering Education, held in Bangkok, Thailand, from 5 to 9 July 2004.

- [20] Amartya Kumar Dutta, "Mathematics in Ancient India", SERIES ARTICLE, SpringerLink, April 2002.

- [21] Jagadguru Swami Sri Bharati Krishna Tirthji Maharaja,"Vedic Mathematics", Book, Motilal Banarsidas, Varanasi, India, 1986.

- [22] Prof. S. Srinivasan, Lecture 15 "ARRAY MULTIPLIER", Lecture series on Digital Circuits & Systems, Department of Electrical Engineering, IIT Madras. http://www.youtube.com/watch?v=5-PI4T25OXI.

- [23] kiat seng yeo, kaushik roy" low voltage low power vlsi subsystems", Book, p.p. 119-144, Mc Graw Hill Professional Engineering, 2005.

- [24] Sameer Palnitkar, "Verilog HDL-A Guide to Digital Design and Synthesis", Book, Sun Soft Press, 1996.

- [25] Stephen D. Brown, and ZvonkoVranesic, "Fundamentals of Digital Logic with Verilog Design, 2nd Edition,", Book McGraw Hill, June, 2007.

- [26] Morris Mano, "Digital circuits and systems", Book, Prentice-Hal, Last updated on-02/27/2011, 11:55.

- [27] Wayne Wolf, "Computer as components", 2nd edition, Book.

- [28] http://en.wikipedia.org/wiki/Verilog

- [29] Xilinx press release, for Xilinix ISE 9.2i, at SAN JOSE, Calif., June 25, 2007. http://www.xilinx.com/prs\_rls/2007/software/0786\_ise92i.htm

- [30] Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Complete Data Sheet, Xilinx, DS083 (v5.0) June 21, 2011.

- [31] Shivakumar M V, Mrs. Anitha Kumari, "A Novel approach towards performance analysis Of Vedic multiplier using FPGA's", International Journal of Electronics, Electrical and Computational System IJEECS ISSN 2348-117X Volume 3, Issue 4 June 2014.

- [32] Sudeep.M.C, Sharath Bimba.M, Mahendra Vucha, "Design and FPGA Implementation of High Speed Vedic Multiplier", International Journal of Computer Applications (0975 – 8887) Volume 90 – No 16, March 2014.

- [33] PushpalataVerma and K.K.Mehta. June 2012. "Implementation of an efficient Multiplier based on Vedic Mathematics using EDA tool.", International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-1, Issue-5, June 2012

- [34] G.Ganesh Kumar, V.Charishma, "Design of High Speed Vedic Multiplier Using Vedic Mathematics Techniques", International Journal of Scientific and Research Publications, Volume 2, Issue 3, March 2012 1 ISSN 2250-3153

- [35] R.Naresh Naik1, P.Siva Nagendra Reddy2, K. Madan Mohan3, "Design of Vedic Multiplier for Digital Signal Processing Applications", International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013

- [36] Gaurav Sharma, Arjun Singh Chauhan, Himanshu Joshi, Satish Kumar Alaria, " Delay Comparison of 4 by 4 Vedic Multiplier based on Different Adder Architectures using VHDL", International Journal of IT, Engineering and Applied Sciences Research (IJIEASR) ISSN: 2319-4413 Volume 2, No. 6, June 2013.

- [37] Mohammed Hasmat Ali, Anil Kumar Sahani, "Study, Implementation and Comparison of Different Multipliers based on Array,KCM and Vedic Mathematics Using EDA Tools", International Journal of Scientific and Research Publications, Volume 3, Issue 6, June 2013 ISSN 2250-3153.

- [38] Krishnaveni D., Umarani T.G., "VLSI IMPLEMENTATION OF VEDIC MULTIP-LIER WITH REDUCED DELAY", International Journal of Advanced Technology & Engineering Research (IJATER) National Conference on Emerging Trends in Technology (NCET-Tech).

- [39] Devika Jaina, Kabiraj Sethi, Rutuparna Panda, "Vedic Mathematics Based Multiply Accumulate Unit", IEEE, 978-0-7695-4587-5/11, 2011.

- [40] S.S. Kerur, Prakash Narchi, Jayashree C N, Harish M. Kittur, Girish V A, "Implementation of Vedic Multiplier for Digital Signal Processing", proceedings published by International Journal of Computer Applications, presented in International conference on Vlsi, Communication and Instrumentation (ICVCI) 2011.

- [41] M. Ramalatha, K. Deena Dayalan, P. Dharani, S. Deborah Priya, "High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques", IEEE, 978-1-4244-3834-1/09, 2009.

- [42] Ramesh Pushpangadan, Vineeth Sukumaran, Rino innocent, Dinesh sasikumar, Vaisak Sundar, "High Speed Vedic Multiplier

for Digital Signal Processors", IETE Journal of Research, Volume 55, Issue 6, Nov-Dec 2009.

- [43] V.K.Karthik, Y.Govardhan, V.Karunakara Reddy, K.Praveena, "Design of Multiply and Accumulate Unit using Vedic Multiplication Techniques", International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013 756 ISSN 2229-5518

- [44] Vaijyanath Kunchigi, Linganagouda Kulkarni, Subhash Kulkarni, "32 Bit MAC unit Design Using Vedic Multiplier", International Journal of Scientific and Research Publications, Volume 3, Issue 2, February 2013 1 ISSN 2250-3153.

- [45] Manoranjan Pradhan, Rutuparna Panda, Sushanta Kumar Sahu, "MAC Implementation using Vedic Multiplication Algorithm", International Journal of Computer Applications (0975 – 8887) Volume 21–No.7, May 2011.