# Design and Simulation of A New Low Power Consumption High Speed Adder For Analog-Digital Circuits

Milad Kaboli<sup>1</sup>, Farhad Amiri<sup>2</sup> <sup>1</sup>Islamic Azad University, Omidieh Branch, Omidieh, Iran <sup>2</sup> Iranian oil pipelines and telecommunications company (ioptc) Kaboli.m@iauo.ac.ir

**Abstract:** Full-adders are the core elements of the complex arithmetic circuits like addition, multiplication, division and exponentiation. Regarding to this importance, new ideas and investigations for constructing full-adders are required.Besides, another fully symmetric full-adder has been presented.In this paper a new high speed and low power adder is presented. The circuit uses a hybrid concept of analog and digital circuit design to propagate the carriage and so achieve a Full Adder with 108 ps delay and 10.12 $\mu$ w of power consumption. Results and simulations demonstrate that the proposed design leads to an efficient full-adder in terms of power consumption. The supply voltage of circuit is 0.65-1.5V and circuit is based on 350 nm CMOS technology (with) using HSPICE.

**Index Terms:** Full Adder, Low Power consumption, Low Voltage, Analog-digital circuit design, Hybrid circuit.

## I. INTRODUCTION

Adders are heart of computational circuits and many complex arithmetic circuits are based on the addition. The vast use of this operation in arithmetic functions attracts a lot of researchers' attentions to adder efficient designs [1, 2]. Nowadays, circuits with low power and high speed have a great importance. Specially regarding to development of mobile systems such as portable computers and cell phones, many researches are dedicated to high speed, low power circuits [3, 4, 6]. Consequently, as a critical part of digital processors, adders are largely studied [3, 6].

??power and have a high speed [7], for some problems such as a long time design procedure [8] they were not developed as processors, in contrast with digital counterparts. However, recently, designers used both concepts of analog and digital circuit design to achieve hybrid processors with positive properties of both analog and digital circuits [9-13]. In this paper also we've used hybrid analog-digital circuits to make an adder with better properties (i.e. with reduced power consumption).

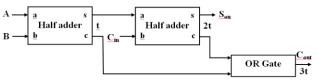

Fig. 1. demonstrates general structure of a full adder; consisting of two half adders and an OR gate. Regardless of implementation details of half adders, they've?? to include at least one gate. With a supposed minimum delay time of t for the gates, simply critical path (the path with maximum delay which determines the overall delay of full adder) can be recognized. it's "carry out" path with 3t delay (shown in Fig.1).

It is also obvious that the minimum of supposed unit time, t, might be the transition delay of a transistor for

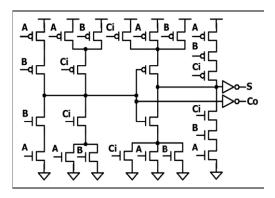

changing the operation mode. Therefore digital full adders will have a valid output at least after three transistor delay time. It is exactly the point where this paper will focus on. It is tried to decrease this delay which in turn will decrease the overall delay time of the Full Adder. To figure out mentioned discussions, a conventional transistor level realization of a CMOS full adder has been inserted in Fig. 2.

Fig. 1. General Structure of a Full Adder and Delay Propagation.

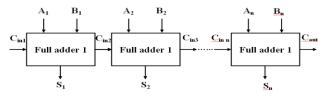

It is noteworthy that also in an *n*-bit adder consisting of *n* full adders, again the carry propagation path is the critical one and determines the overall delay (Note Fig. 3). Names of different adders (Carry Save Adder, Carry Look ahead and so forth) in the literature [1, 14] witnesses the importance of carry propagation and the amount of works dedicated to.

Fig. 2. Conventional CMOS Full Adder

This paper is organized as follow; In the next section the new proposed hybrid analog-digital adder will be presented.

The third section is dedicated to simulation, while the fourth one includes discussions and comparisons. Finally, the fifth section concludes the paper.

Fig. 3. Critical Path Delay; Carry Propagation is very deterministic II. CIRCUIT DESCRIPTION

1. Effective Factors in Power Consumption:

In CMOS digital circuits, average power consumption Pav, in general, as the following expression :

$$P_{AV} = \alpha.c.f.V_{dd}^{2} + P_{SC} + I_{Leakage} \cdot V_{dd}$$

(1)

In this relation Vdd is supply voltage,  $\alpha$  is Statistical rate signal changes, C is capacitance equivalent and f is Work-frequency circuit. Also Ileakage is leakage current and Psc is short circuit power. Last component in the right relationship (1) is power related to leakage currents. Leakage currents to three components flow below threshold leakage, gate leakage current and leakage current of bayas reverse source–drain junctions, are divisible. Source-drain current of transistor in model BSIM, is expressed as follows:

$$I_{DS} = I_0 e \frac{V_{GS} - V_{th0} + \gamma V_{BS} + \eta}{n V_T} \quad (1 - e^{-V_{DS} / V_T})$$

(2)

In this Relation,  $V_T$  is the thermal voltage and  $V_{GS}$ ,  $V_{DS}$  and  $V_{BS}$  are respectively gate-source voltages, drainsource voltage and Body-source voltage. Parameters  $\gamma$  and  $\eta$  are respectively, body effect coefficient and DIBL effect coefficient and n coefficient is slope of the below the threshold. I<sub>0</sub> value is also defined as follows:

$$I_0 = \mu_0 C_{OX} W_{eff} / L_{eff} V_T^2 e^{1.8}$$

(3)

In this relation,  $\mu_0$  is the electron mobility coefficient,  $C_{OX}$  is Capacitance per unit area gate oxide layer,  $W_{eff}$ and  $L_{\text{eff}}$  are the Effective channel length and width of the transistor and  $V_T$  is the thermal voltage. Relation (2) shows that in the turn off transistors ( $V_{GS}=0$ ), drainsource current value is greater than zero. This current, leakage current below threshold is called??. In transistors with a channel length 130 nm and more, leakage currents are small and can be venial. In transistors with smaller dimensions, which also reduced the working voltage to maintain the circuit speed, it is also necessary for threshold voltage to be reduced. Relation (2) shows that leakage current below the threshold with the threshold voltage reduces as exponential increases. In the dimension reduction process, the gate oxide thickness for more control channel, is reduced. Decrease of the oxide thickness, increase of probability of quantum tunneling electron and hole from potential barrier oxide layer are along. Effect of this possibility increase will be as leakage current that will be established between the gate and heads of drain, source, channel and body. Whatever the gate oxide thickness less ??and Gate potential differences with other areas is more, This measure of current is increased [22]. leakage current of reverse Bias source-drain junction is low range and venial. In circuits with high density, Power consumption due to leakage currents A large percentage of the total power consumption makes up and with smaller dimensions is expected amount and percentage increase in the future to be more. Therefore, in designing and modeling digital circuits, it is necessary to consider the effect of leakage currents as determines parameter.

2. Reduce Power Consumption With Control Leakage Current:

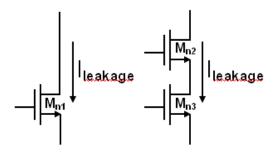

Several methodes for leakage current reduction have been proposed. Some methods are used only in passive circuit conditions and some other decrease leakage currents in all cases. Relation (2) shows that increase potential of source in off transistor causes the leakage current reduction. One of the ways to achieve this state, is using a series switched-off transistor. In Figure 4 leakage current and loss resulting thereform, increases source\_potential in the transistor MN2. So leakage current of two off series transistor is much less than leakage current of off transistor MN1 [23]. With Replacing a transistor with two series transistor , Leakage current will be low, but Against speed of circuit will be low or space consumption increases.

Fig. 4. Reducing leakage current in cut off transistors

Using transistors with different threshold voltage is another effective method in controlling leakage current. Transistors with low threshold voltage have low delay and high leakage current. Unlike High threshold voltage transistors which are with larger delay, Leakage current is less. The best place to use this type of transistor is known with Separation of different input and output ways of circuit to critical and uncritical. In the critical paths total of path delay is equal with maximum allowable value or very close to it, but in uncritical paths total of path delay is smaller than the Maximum allowable Value.As regards, usually the number of critically paths in digital circuits is low, placing a low threshold voltage transistors in the critical paths and high threshold voltage transistors in the uncritical paths, speed of circuit is fixed, but current leakage can decrease power consumption. In MOS transistors the effective threshold voltage transistors are described using the following equation:

$$V_{th} = V_{th0} + \gamma V_{BS} - \eta V_{DS}$$

(4)

In this relation  $V_{TH0}$  is initial threshold voltage,  $V_{SB}$  is source-body voltage,  $V_{DS}$  is drain-source voltage and the parameters  $\gamma$  and  $\eta$  respectively are coefficients of body and DIBL effects. Based on the relation, there is a direct relationship between effective threshold voltage with coefficient  $\gamma$  and body voltage difference to the source. In another way, reduced power consumption that inversebias of body is called by change potential of body, increase effecting threshold voltage and leakage current is less???. Needed changes to control the affecting threshold voltage is in type n, the more negative is the body potential than the source and in the p type transistors, the more positive is body potential than the source.

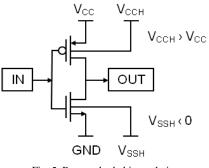

Fig. 5. Reverse body bias technique

Considering the reduced speed of circuit with increase threshold voltage, in another way it is considered connected to the transistor body in two different potentials. In the moments that higher speed is desirable. node of body Transistor respectively is connected to GND and V<sub>CC</sub> which is less than threshold voltage. With this work, circuit delay is less but leakage current increases. In the Moments that higher speed is not required, body respectively is connected to V<sub>SSH</sub> and V<sub>CCH</sub> than??? increase threshold voltage and reduced leakage current. A problem existing in this method is production of needed reverse potential and possible availability of the node body transistors. Another method that is effective in reducing leakage current by adding the channel length (Leff)??. With Increased Channel length, the transistor Power Consumption reduces and the speed with the reduced linear track, but against the Leakage current decreases with exponentially rate. 3. Proposed Analog-Digital Circuit:

### A. Carry propagation:

In this section we introduce a new design style, entitled "bridge". Bridge circuits are circuits that create a conditional conjunction between two circuit nodes. Using this kind of circuits the classical circuits can be implemented faster and smaller than the conventional. As mentioned before, conventional CMOS design style performs realizations by organizing some different branches. Each branch provides a path from supply lines to an output, whereas bridge design style focuses its attention on meshes, and connects each two adjacent mesh by a transistor, named "bridge transistor". Bridge transistors provide the possibility of sharing transistors of different paths to create a new path from supply lines to an output. These transistors must be arranged in such a way that not only validate the correctness of the circuit, but also preserve pull-up and pull-down networks mutually exclusive. In general, bridge style can lead to very structured designs. In this style control signals can be applied to the sides of meshes [15,20].

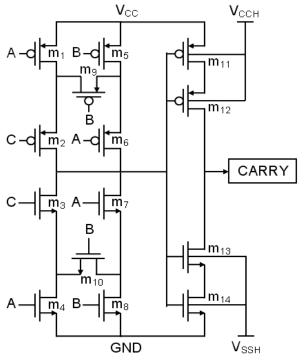

Figure 6 illustrates a bridge implementation of the three inputs majority function (or carry generator). The transistors in grey boxes (Figure 6) are bridge transistors. This structure uses 14 transistors to implement the relevant function. With respect to high flexibility of bridge methodology, variants of logic circuits can be easily realized. In this design it has been tried to have a symmetric structure in both pull up and pull down networks. In order to construct a full-adder, two different parts are required. Carry part implementation has been performed as Figure 6.

Fig. 6. A symmetric structure for carry generator In this figure  $m_{12}$  and  $m_{13}$  are series transistors with  $m_{11}$ and  $m_{14}$  to decrease leakage current and power consumption. Also in transistors  $m_{11}$ ,  $m_{12}$ ,  $m_{13}$ ,  $m_{14}$  body

nodes are connected to  $V_{CCH}$  and  $V_{SSH}$  to increase  $V_T$  and decrease leakage current and power consumption. B. Sumation:

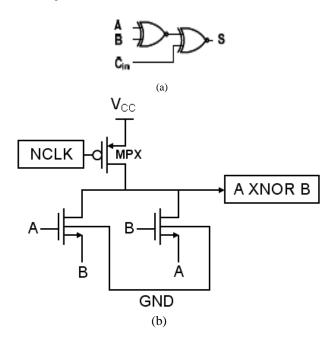

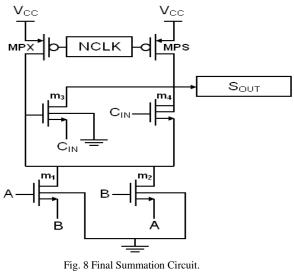

For summation a simple digital circuit consisting of two XNOR gates has been used to produce output summation as in Fig. 7-(a).

Fig. 7 (a) Digital Circuit for Summation, (b) XNOR circuits used in part (a).

XNORs of Fig. 7-(a) are implemented by circuit shown in Fig. 7-(b). When both inputs are high, or low, both transistors would be in cut-off and so the output remains at high level which was pre-charged to. If one of the inputs is high and the other is low, then one of the transistors (which has a gate node at high level and source at low level) will be in saturation and discharges the output node. Therefore the final circuit of summation was implemented as demonstrated in Fig.8.

III. SIMULATION

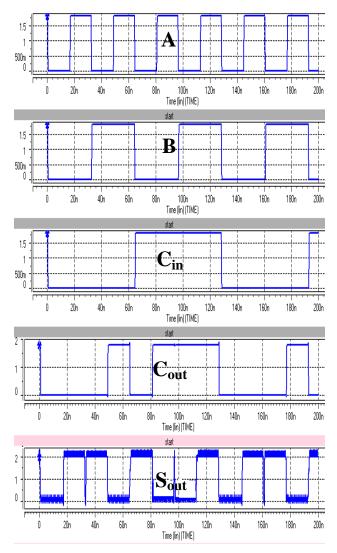

To study performance of the proposed circuit, it was simulated on HPICE, with the  $0.35_{\mu m}$  TSMC at room

temperature with supply voltage ranges from 0.65v to 1.5v. As one of the properties of used technology, the minimum width and length of transistor are respectively 0.60 $\mu$ m and 0.45 $\mu$ m,. Figure 9 shows input signals of A, B, C<sub>in</sub> and output signals of S<sub>out</sub> and C<sub>out</sub>.

Fig.9. Simulation results for different inputs of the proposed Full Adder.

# **IV. CONCLUSION**

The supply voltage of circuit is 0.65-1.5V and circuit is based on 350 nm CMOS technology (with) using HSPICE. Other simulation values are shown in Table 1.

| Number of MOS     | 20        |

|-------------------|-----------|

| Supply            | 0.65-1.5V |

| power consumption | 10.12 µw  |

| Delay             | 108 ps    |

## TABLE I

#### SPECIFICATION OF CIRCUIT

#### REFERENCE

- [1] J. Rabaey, Digital Integrated Circuits (A Design Perspective), Prentice-Hall, Englewood Cliffs, NJ, 1996.

- [2] A. Chandrakasan, W. Bowhill, F. Fox (Eds.), "Design of High-Performance Microprocessor Circuits", IEEE Press, New York, 2001.

- [3] C. Tung, Y-C. Hung, S-H. Shieh and G-S. Huang, "A Low-Power High-Speed Hybrid CMOS Full Adder for Embedded System", IEEE Proc. No. 1-4244-1161, 2007.

- [4] Jiang, Y.; AI-Sheraidah, A.; Wang, Y.; Sha, E.; Chung, J.-G.: "A Novel Multiplexer-Based Low-Power Full Adder". IEEE Transactions on Circuits und \$vsmn -13: Eqress Brie@, Volume 51, NO. 7, pp. 345 - 348, Jul. 2004.

- [5] C.-H. Chang, J. Gu, M. Zhang, "A Review of 0.18-um full adder performances for tree structured arithmetic circuits", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.13,pp. 686 – 695, Issue 6, June 2005.

- [6] S. Goel, S. Gollamudi, A. Kumar, M. Bayoumi, "On the design of low energy hybrid CMOS 1-bit full adder cells", in Proc. of the 2004 47th Midwest Symposium on Circuits and Systems, vol.2, pp.209 - 212, July 2004.

- [7] W. Wang, D. Jin, "Neuro-fuzzy system with high-speed low-power analog blocks", Fuzzy Sets and System, Vol. 157, 2006.

- [8] Yu-Tsun Chien and colleagues, "SPEED: Synthesis of High performance Large Scale Analog/Mixed Signal circuits", 2005.

- [9] M. Mirhassani, M. Ahmadi, W. C. Miller, "A feed-forward timemultiplexed neural network with mixed-signal neuronsynapse arrays", Microelectronic Engineering, Vol. 84, pp. 300-307, 2007.

- [10] Y. Horio, T. Ikeguchi, K. Aihara, "A mixed analog/digital chaotic neuro-computer system for quadratic assignment problems ", Neural Networks, Vol. 18, 2005.

- [11] R. Karakiewicsz, R. Genov, G. Cauwenberghs, "480-GMACS/Mw Resonant Adiabatic Mixed-Signal Processor Array for Charge-Based Pattern Recognition", IEEE Journal of Solid-State Circuits, Vol. 42, No. 11, November 2007.

- [12] S. Badel, A. Schmid, Y. Leblebici, "CMOS realization of twodimensional mixed analog-digital Hamming distance discriminator circuits for real-time imaging applications", Micro Electronics Journal, 2008.

- [13] N. Taherinejad, H. S. Shah hosseini, "A new Digital Multiplier/Divider Architecture, Via Hybrid Analog-Digital Processing", IEEE Proc. Of Mixdes Conference, pp. 181-185, June 2008.

- [14] N. H. E. Weste and K. Eshraghian, "Principles of CMOS VLSI design", Addison Wesley, 1993.

- [15] K. Navi, O. Kavehei, M. Rouholamini, A. Sahafi, S. Mehrabi, N. Dadkhahi, "Low-Power and High- Performance 1-bit CMOS Full-Adder Cell," Journal of Computers, Academy Press, Accepted.

- [16] F.Vasefi, Z. Abid, "Low Power N-Bit Adders and Multiplier using lowest-number-of-transistor 1-bit adders", IEEE Proc. Of CCECE/CCGEI Saskatoon, May 2005.

- [17] C. K. Tung, Y. C. Hung, S. H. Shieh, G. S. Huang, "A Low-Power High-Speed Hybrid CMOS Full Adder for Embedded System", IEEE No. 1-4244-1161, 2007.

- [18] M. Alioto, G. Di Cataldo, G. Palumbo, "Mixed Full Adder topologies for high-performance low-power arithmetic circuits", Microelectronics Journal, Vol. 38, p.p 130–139, 2007.

- [19] Z. Abid, H. El-Razouk, D.A. El-Dib, "Low power multipliers based on new hybrid full adders", Microelectronics Journal (In Press), 2008.

- [20] K. Navi, O. Kavehie, M. Rouholamini, A. Sahafi, S. Mehrabi, "A Novel CMOS Full Adder," 20<sup>th</sup> International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07), India, pp. 303-307, Jan. 2007.

- [21] O. Kavehie, K. Navi, E. Afjei, H. Khorsand, "Minimization of Multiple-Valued Decision Diagrams Based on Matrix Computation," American Journal of Applied Sciences, Accepted.

- [22] single threshold CMOS," in Proc. ACM/IEEE Design Automation.

- [23] S. Heo, K. Barr, M. Hampton, and K. Asanovic, "Dynamic finegrain leakage reduction using leakage-biased bitlines," in ACM SIGARCH Computer Architecture News, vol. 30.