# Design and Implementation of Testable Reversible Sequential Circuits and Garbage Output

[1] M.PREETHA, [2] P.AMUTHINI.

Prathyusha Institute of Technology And Management [1]-ASSISTANT PROFESSOR, EEE, preethavalli@gmail.com [2]-ASSISTANT PROFESSOR, EEE, pamuthini@gmail.com

Abstract— The conservative reversible gates are used to designed reversible sequential circuits. The sequential circuits are flip flops and latches. The conservative logic gates are Feynman, Toffoli, and Fredkin. the design of two vectors testable sequential circuits based on conservative logic gates. All sequential circuit based on conservative logic gates can be tested for classical unidirectional stuck-at faults using only two test vectors. The two test vectors are all 1s, and all 0s. The designs of two vectors testable latches, master-slave flip-flops and double edge triggered (DET) flipflops are presented. We also showed the application of the proposed approach toward 100% fault coverage for single missing/additional cell defect in the quantum- dot cellular automata (QCA) layout of the Fredkin gate. The conservative logic gates are in terms of complexity, speed and area.

*Index Terms*— Reversible Logic, Sequential Circuits, Quantum dot Cellular Automata, D-Latch, Barrel Shifter

#### **I.INTRODUCTION**

Conservative logic is called reversible conservative logic when there is a one-to-one mapping between the inputs andthe outputs vectors along with the property that there are

equal number of 1s in the outputs as in the inputs. Conservative logic circuits are not reversible, if one-toone mapping between the inputs and the outputs vectors is not preserved Conservative logic can be reversible in nature or may not be reversible in nature. Reversibility is the property of circuits in which there is one to- one mapping between the inputs and the output vectors, that is for each input vector there is a. unique output vector vice-versaQCA is one of the emerging and nanotechnologies in which it is possible to implement reversible logic gates. QCA makes it.possible to achive circuit densities and clock frequencies be yond the limits of existing CMOS technology. In QCA, computing logic states of 1 and 0 are represented by the position of the electrons inside the QCA cell. Thus, when the bit is flipped

from 1 to 0 there is no actual discharging of the capacitor as in conventional CMOS. Hence, QCA does not have to dissipate all its signal energy during transition. Further, propagation of

the polarization from one cell to another is because of interact-tion of the electrons in adjacent QCA cells. As

there is no movement of electrons from one QCA cell to the other, there is no current flow. Therefore, QCA has significant advantage compared to CMOS technology in terms of power dissipation.

Due to high error rates in nano-scale manufacturing,QCA and other nanotechnologies target reducing device error rates. This paper is organized as follows. Section II presents the

conservative logic gates, Section III presents design of testable reversible latches, Section IV describes QCA, section V presents design of testable reversible flip-flop section VI discusses the application of the proposed two vectors, all 0s and all 1s, Section VII provides some discussions and conclusions.

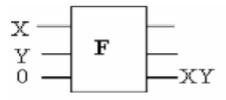

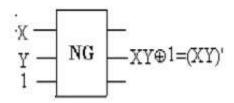

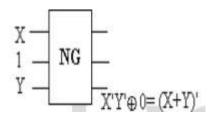

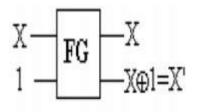

**2 CONSERVATIVE LOGIC GATES** In order to design the sequential circuits, the conventional logic gates are appropriately designed from the reversible gates. The reversible gates used to design the conventional

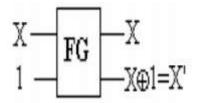

logic are so chosen to minimize the number of reversible gates used and garbage outputs produced . The design of AND function using Fredkin gate. The design of NAND and NOR function using New Gate respectively Feynman Gates can be used for copying the outputs and to avoid the fan out problem in reversible logic . In the Feynman gate, there are exactly two outputs corresponding to the inputs and a '0' in the second input will copy the first input to both the outputs of that gate. Hence it can be concluded that Feynman gate is the most suitable gate for single copy of bit since it does not produces any garbage output. The Feynman gate as copying output and

garbage output. The Feynman gate as copying output and NOT function respectively. May stuck at 0 or 1 leading to accessing wrong address, no address, or multiple addresses.

Fig.1 Fridkin Gate As AND Gate

Fig.2 new Gate As NAND Gate

Fig.3 new Gate As NOR Gate

Fig.4 Feynman Gate As copying output

Fig.5 Feynman Gate As NOT Gates

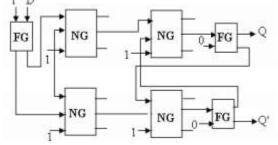

Novel Reversible Flip Flops are designed using Feynman Gate, New gate and Fredkin Gate. The designed FFs are highly optimized in terms of number of reversible gates and garbage

outputs. Reversible logic elements, both with and without the property of conservatism, can be defined in many different logic systems. For the purposes of this paper, the class of reversible elements that can be modeled as binary-valued logic circuits will be called classical reversible logic.

| $x^+ = x$                       | TOF3(x,y,z) |

|---------------------------------|-------------|

| $y^+ = y$                       |             |

| $z^+ = xy \oplus z$             |             |

| $x^+ = x$                       | FRE(x,y,z)  |

| $y^+ = \overline{x}y \oplus xz$ |             |

| $z^+ = \overline{x}z \oplus xy$ |             |

Table 1. Gate Functionality

#### **3 DESIGN REVERSIBLE LATCHES**

The characteristic equation of the D latch can be written as  $Q+ = D \cdot E + .E \cdot Q$ . In the proposed work, enable (E) refers to the clock and is used interchangeably in place of clock. When the enable signal (clock) is 1, the value of the input D is reflected at the output that is Q+ = D. While, when E = 0 the latch maintains its previous state, that is Q+ = Q. The reversible Fredkin gate has two of its outputs working as 2:1 MUxes, thus the characteristic equation of the D latch can be mapped to the Fredkin gate (F). The realization of the reversible D latch

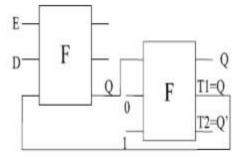

using the Fredkin gate. But FO is not allowed in conservative reversible logic. Moreover, the design cannot be tested by two input vectors all 0s and all 1s because of feedback, as the outputput Q would latch 1 when the inputs are toggled from all 1s to all 0s and could be misinterpreted as stuck-at-1 fault. In this paper, we propose to cascade another Fredkin gate to output Q as shown in Fig. The design has two control signals, C1 and C2. The design can work in two modes: normal mode and test mode.

#### 3.1 NORMAL MODE

The normal mode is shown in Fig. in which we will have C1C2 = 01 and we will have the design working as a D latch without any fan-out problem.

Fig.6 Fredkin gate based D-latch in normal mode: c1=0 and c2=1.

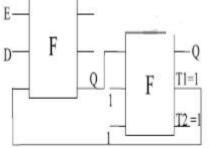

3.2 TEST MODE

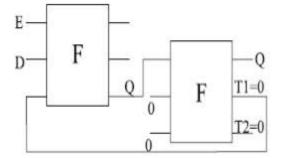

In test mode, when C1C2 = 00 as shown in Fig. it will make the design testable with all 0s input vectors as output T1 will become 0 resulting in

Thus, any stuck-at-1 fault can be detected When C1C2 = 11 as shown in Fig. the output T1 will become 1 and the design will become testable with all 1s input vectors for any stuck-at-0 faulte. It can seen from above that C1 and C2 will

disrupt the feedback in test mode, and in normal mode will take care of the fan-out Thus, our proposed design works as a reversible D latch and can be tested with only two test vectors,

all 0s and all 1s, for any stuck-at fault by utilizing the inherent property of conservative reversible logic.

Fig.7 Fredkin gate based D-latch in test mode for stuck-at-0 fault c1=1 and c2=1.

Fig.7 Fredkin gate based D-latch in test mode for stuck-at-1 fault c1=0 and c2=0.

# 4 QUANTUM-DOT CELLULAR AUTOMATA

Ouantum-dot cellular automata (OCA) is а nanotechnology that has recently been recognized as one of the top six emerging technologies with potential applications in future computers. Several studies have reported that QCA can be used to design general-purpose computational and memory circuits. First proposed in 1993 by Lent et a, and experimentally verified in 1997, QCA is expected to achieve high device density, extremely low power consumption, and very high switching speed The fundamental QCA logic primitives are the three-input majority gate, wire, and inverte Each of these

can be considered as a separate QCA locally interconnected structure, where QCA digital architectures

are combinations of these cellular automata structures. Traditional logic reduction

methods, such as Karnaugh maps (K-maps), always produce simplified expressions in the two standard forms: sum of products (SOP) or product of sums (POS) However, we will encounter difficulties in converting these two forms into a majority expressions due to the complexity of multilevel majority

gates. In CMOS/silicon design, the logic circuits are usually implemented using AND, OR gates based on SOP or POS fomats. However, since QCA logic is based on a majority gate

primitive, it is critical that an efficient technique be established for designing with this primitive. In this paper, we develop a Boolean algebra based on a geometrical interpretation of three-variable Boolean functions to facilitate the conversion of sum-of-products expressions into reduced majority logic.thirteen standard functions are introduced, which represent all possible three-variable Boolean functions. For each of these standard functions. we present the reduced majority expression. As an example of this technique, we present a QCA adder design, and show that proposed method it is able to be reduce the total hardware, as compared to previously published designs.

### 4.1 QCA LOGIC DEVICES

The fundamental QCA logic primitives include a QCA wire, QCA inverter, and QCA majority gate, as described below.

Fig.9 QCA inverter

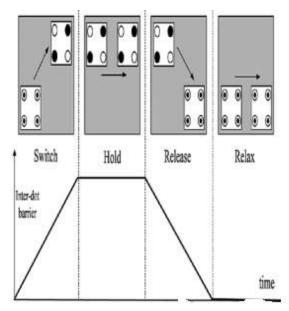

4.2 QCA CLOCK

A QCA clock consists of four phases which are called Switch, Hold, Release, and Relax as shown in Fig. During the Switch phase, the inter dot barriers are slowly raised and the QCA cells become polarized according to the state of their drivers (that is, their input cells). During the Hold phase, the interdot barriers are kept high and the QCA cell retain their states.

Fig.foure phases of aQCA clocks

In the Release phase the barriers are lowered and the cells are allowed to relax to an unpolarized state. Finally, in the Relax phase, the barriers are kept low and the cells remain unpolarized A QCA circuit is partitioned into serial zones. These zones can be of irregular shape, but their size must be within certain limits imposed by fabrication and dissipation concerns. All cells in the same zone are controlled by the common clock signal. The scheme of clock zones per mits an array of QCA cells to make a certain calculation and then have its state frozen, and finally, have its output serve as the input to the next clock zone.

### **5 REVERSIBLE FLIP-FLOP**

The D flip flop is a modification of the clocked RS flip flop. In the D flip flop, the D input goes directly to the S input and its complement is applied as an R input. The D flip flop designed from irreversible gates. The D flip flop designed from the reversible equivalent gates. The proposed circuit of the flip flop is evaluated in terms of number of reversible gates used and garbage outputs produced.

Fig.11 Revisible D flipflop

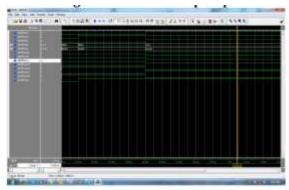

Fig.12.Output for reversible D-flipflop

## 6 TESTING APPROACH TO QCA COMPUTING

QCA computing provides a promising technology to implement reversible logic gates.

The QCA design of Fredkin gate using the four-phase clocking scheme in which the clocking zone is shown by the number next to D (D0 means clock 0 zone, D1 means clock 1 zone, and so on). It can be seen that the Fredkin gate has two level MV implementation, and it reduced quires 6 MVs and four clocking zones for implementation. the number of clocking zones in a OCA circuit represents. the delay of the circuit (delay between the inputs and the outputs). Higher the number of clocking zones, lower the operating speed of the circuit. In QCA manufacturing, defects can occur during the synthesis and deposition phases, although defects are most likely to take place during the deposition phase. researchers have shown that QCA cells are more susceptible to missing and additional QCA cell defects. The additional cell

defect is because of the deposition of an additional cell on the substrate. The missing cell defect is due to the missing of a particular cell. Researchers have been addressing the design and test of QCA circuits assuming the single missing/additional cell defect model.

#### 7 CONCLUSION

Therefore conservative reversible logic gates are used to designed sequential circuits. The proposed system is used in the Feynman gate. This paper proposed reversible sequential

circuits based on conservative logic that is testable for any unidirectional stuck-at faults using only two test vectors, all 0s and all 1s. The proposed sequential circuits based on conservative logic gates outperform the sequential circuit implemented in classical gates in terms of testability The sequential circuits implemented using conventional classic gates do not provide inherited support for testability. Hence, a conventional sequential circuit needs modification in the original circuitry to provide the testing capability Also as the complexity of a sequential circuit increases the number of test vector required to test the sequential circuit also increases. For example, to test a complex sequential circuit thousand of test vectors are re quired to test all stuck-at-faults, while if the same sequential

circuit is build using proposed reversible sequential building blocks it can be tested by only two test vectors, all 0s and all 1s. Thus, the main advantage of the proposedconservative reversible sequential circuits compared to the conventional sequential circuits the need of only two test vectors to test any sequential circuit irrespective of its complexity, the reduction in number of test vectors minimizes the overhead of test time for a reversible sequential circuit. The proposed work has the limitation that it cannot detect multiple stuck-at-faults as well as multiple missing/additional cell defects. In conclusion, this paper advances the state-of-the-art by minimizing the number of testas single missing/additional cell defects. vectors needed to detect stuck-at-faults as well as single missing/additional cell defects.

## ACKNOWLEDGMENT

The authors are thank full to N.Bamakumari for his encouragement and support in publishing of this paper and are also highly thankful to management of prathyusha institute of technology and managementfor their financial support.

**8 REFERENCES**

[1] J. Ren and V. K. Semenov, "Progress with physically and

logically reversible superconducting digital circuits," IEEE

Trans. Appl. Super- conduct., vol. 21, no. 3, pp. 780–786, Jun.2011

[3] H. Thapliyal and N. Ranganathan, "Reversible logic-based

concurrently testable latches for molecular QCA," IEEE Trans.

Nanotechnol., vol. 9, no. 1, pp. 62-69, Jan. 2010.

[2] S. F. Murphy, M. Ottavi, M. Frank, and E. DeBenedictis,

"On the design of reversible QDCA systems," Sandia National

Laboratories, Albuquerque, NM, Tech. Rep. SAND2006-5990,

2006.

[4] p.Tougaw and C. Lent, "Logical devices implemented using quantum cellular automata," J. Appl. Phys., vol. 75, no. 3, pp. 1818–1825, Nov. 1994.

[5] M. Hasan, A. Islam, and A. Chowdhury, "Design and analysis of online testability of reversible sequential circuits,"

in Proc. Int. Conf. Comput. Inf. Technol., Dec. 2009, pp. 180–185.

[6]H. Thapliyal and N. Ranganathan, "Design of reversible

sequential circuits optimizing quantum cost, delay and garbage outputs," ACM J. Emerg. Technol. Comput. Syst., vol. 6, no. 4, pp. 14:1–14:35, Dec. 2010

[7] S. Mahammad and K. Veezhinathan, "Constructing online testable circuits using reversible logic," IEEE Trans. Instrum.

Meas., vol. 59, no. 1, pp. 101–109, Jan. 2010

[8]H. Thapliyal, M. B. Srinivas, and M. Zwolinski, "A begining in the reversible logic synthesis of sequential circuits," in proc. Int. Conf. Military Aerosp. Program. Logic Devices,

Washington, DC, Sep. 2005, pp. 1-5.

[9]P.Kartschoke, "Implementation issues in conservative logic networks," M.S. thesis, Dept. Electr. Eng., Univ. Virginia, Char lottesville, 1992. [10] G. Swaminathan, "Concurrent error detection techniques using parity," M.S. thesis, Dept. Electr. Eng.,

Univ. Virginia, Charlottesville, 1989.

[10] E. Fredkin and T. Toffoli, "Conservative logic," Int. J. Theor.

Phys., vol. 21, nos. 3-4, pp. 219-253, 1982.

[11] G. Swaminathan, J. Aylor, and B. Johnson, "Concurrent

testing of VLSI circuits using conservative logic," in Proc. Int.

Conf. Comput. Design, Cambridge, MA, Sep. 1990, pp. 60-65.

[12] P. Tougaw and C. Lent, "Dynamic behavior of quantum

cellular automata," J. Appl. Phys., vol. 80, no. 8, pp. 4722-4736,

Oct. 1996. [6] M. B. Tahoori, J. Huang, M. Momenzadeh, and F.

Lombardi, "Testing of quantum cellular automata," IEEE

Trans. Nanotechnol., vol. 3, no. 4, pp. 432–442, Dec. 2004