# Bypassing Technique Based Braun Multiplier for Low Power Consumption with Improved Speed

Kusum Sahu<sup>#1</sup>, Rahul Sinha<sup>\*2</sup>

<sup>#</sup>Electronics and Telecommunication, CSVTU CSIT Durg (C.G.), India

<sup>1</sup>kusum.sahu13@gmail.com

\* Electronics and Telecommunication, CSVTU CSIT Durg (C.G.), India

<sup>2</sup>rsinha.vlsieng@gmail.com

Abstract— A multiplier is one of the key hardware blocks in most digital and high performance systems such as FIR filters, digital signal processors and microprocessors etc. If the power consumption of the multiplier block reduced, then reduction of the power consumption of various digital signal processing chips and communication systems could be possible. In this paper 4/8/16 bit Braun multiplier has been designed using bypassing technique and a comparative study of all bypassing techniques on the basis of their power consumption is done. At the last stage of the multiplier KSA (Kogge Stone Adder) and RCA (Ripple Carry Adder) is used for high speed and the low power consumption. The implementation of Braun multipliers and its bypassing techniques is done using Verilog HDL Xilinx 14.4 ISE and it is verified using the Spartan6, device xc6slx45. After comparing, it is concluded that mixed bypass multiplier is best suited for situations where both delay and power are low. The number of slices & LUT used is also less when compared to other techniques. For 16 bit Row and Column Bypassing Technique using KSA the delay and power found to be 28.118 ns and 0.184 Watt From other two methods (Row Bypass and Column Bypass) it is found to be (28.679ns & 0.190 Watt) and (28.518 ns and 0.184 Watt) respectively.

# *Keywords*— Column Bypass, KSA, Mixed Bypass, RCA, Row Bypass, Verilog HDL.

### I. Introduction

Multiplication is one of the essential operations in Digital Signal Processing (DSP) applications like Fast Fourier Transform (FFT), Digital filters etc. [1]. In DSP applications, most of the power is consumed by the multipliers, hence low power multipliers must be designed in order to reduce the power dissipation in DSP applications. With advancement in the technology, many investigators have examined and are trying to design multipliers which will offer the following design characteristic - Accuracy, low power consumption, high speed, regularity of layout, less complexity and less area or the combination of all these characteristic in one multiplier thus making them appropriate for several low power consumption, high speed, less area in compact VLSI implementation. The multiplication is an arithmetic operation for common DSP application, such as digital filter, digital microprocessor, Fast Fourier communication system, Transform (FFT), portable and battery operated devices. In order to achieve the high speed and low power demand in DSP applications, parallel array multipliers are generally used. One such commonly used parallel array multiplier is the Braun's multiplier. The Braun's multiplier is generally called

as the CSA (Carry Save Array Multiplier). The architecture of a Braun's multiplier consists of AND gates and full adders. Power consumption is mainly due to the Static and Dynamic power consumption. Static power consumption is very small so our major concern is the Dynamic power Consumption which have to be reduced using Braun Multiplier so that our portable devices will have a long life. When Braun multiplier is used without Bypassing technique then power consumption can be increased this disadvantage can be removed by using Braun multiplier using bypassing technique and at the last stage of the bypassing based multiplier KSA and RCA can be used to improve the switching speed and for the low power consumption.

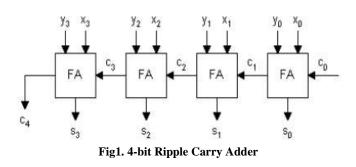

## II. The Adders

**Ripple Carry Adder** Ripple carry adder can be designed by cascading full adder in series i.e. carry from previous full adder is connected as input carry for the next stage [1]. Multiple full adder circuits can be cascaded in parallel to add an N-bit number. For a 4- bit parallel adder, there must be 4 number of full adder circuits. A Ripple Carry Adder is a logic circuit in which the carry-out of each full adder. It is called a Ripple Carry Adder because each carry bit gets rippled into the next stage. In a Ripple Carry Adder the sum and carry out bits of any Half Adder stage is not valid until the carry in of that stage occurs.

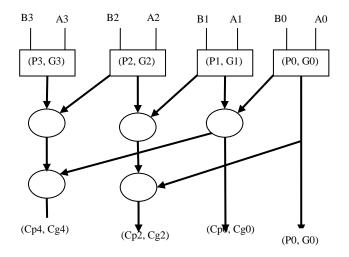

**Kogge Stone Adder** The Kogge-Stone Adder concept was given by Peter M. Kogge and Harold S. Stone and was published in 1973. In Ripple Carry Adder the carry input of Full Adder is dependent on the carry output of the previous Full Adder and present Full Adder wait until the previous Full Adder has generated output. Hence delay is more for the Ripple Carry Adder if no. of bit increases, then delays also

increases, so for reducing this delay Kogge Stone Adder (KSA) is used. Three computational stages are used in Kogge Stone Adder these are Preprocessing, Carry generation network, Post processing.

Fig2. 4 bit Kogge Stone Adder

## III. Bypassing Technique

Bypassing means to turn off some row or column when their outputs are known or in other words, we can say that Row or Column may be turn off when either multiplicand or multiplier or both bits have zero value. To reduce the switching activities three types of bypassing techniques are used in this project these are: -

- Row bypassing multiplier

- Column bypassing multiplier

- Row and Column bypassing multiplier

The Basic building blocks used for the construction of all these Bypassing based multiplier is FA cell (Full Adder cell). This Full Adder cell is constructed by using one Full Adder, Multiplexers and Buffers.

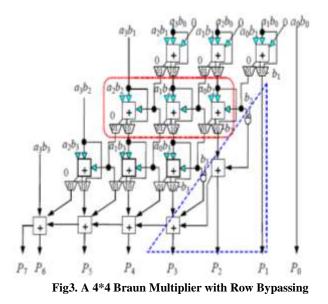

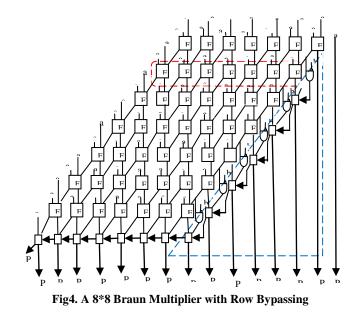

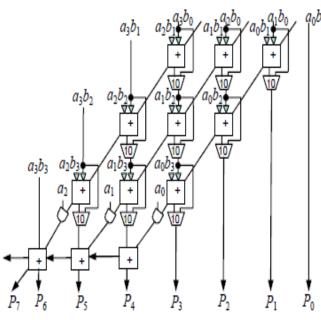

#### **IV.** Row Bypassing Multiplier

In Row bypassing multiplier if multiplier bit  $b_2$  is zero in below figure then partial products output is directly given to the third row from the first row and the second row is disabled. But when the rightmost full adder in the second row is disabled then addition is not executed and it would not give a correct answer so some extra circuitry is required which is shown in the triangle area. This is the drawback of Row Bypassing Multiplier.

One of the drawbacks of this Row bypassing Braun multiplier is that if the rightmost FA cell in the second row is disabled then it would not give a correct result, so to obtain an accurate result in some extra circuitry is required which is shown in the above figure enclosed by the blue triangle area. This drawback can be reduced by using a Column bypassing multiplier.

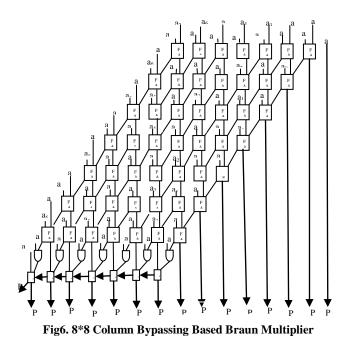

# V. Column Bypassing Multiplier

The drawback of the Row Bypassing technique can be minimized by using column bypassing multiplier and it is used when multiplicand bit is zero. To design 4\*4, 8\*8 and 16\*16 bit Braun multiplier with Column bypassing, the basic building block is FACELL (Full adder cell). This FACELL can be designed by using full adder, multiplexer, buffer. A 4\*4 column bypassing multiplier can be implemented by using (n-1)\*(n-1) full adders, (n-1)\*(n-1) multiplexers and 2\*(n-1)\*(n-1) buffers.

Fig5. 4\*4 Column Bypassing Based Braun Multiplier

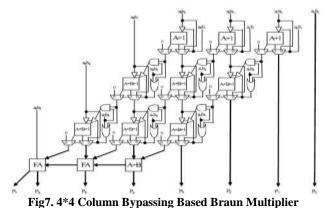

### VI. Row and Column Bypassing

In mixed bypassing multiplier the addition operations in the ith column or the j-th row can be bypassed if the  $a_i$  bit in the multiplicand is 0 or the  $b_j$  bit in the multiplier is 0. The basic building block for the designing a 4\*4 Row and Column bypass multiplier is FA cell and it can be implemented by using (n-1)\*(n-1) full adders, 2\*(n-1)\*(n-1) multiplexers and 2\*(n-1)\*(n-1) buffers.

Fig7. 4\*4 Column Dypassing Dased Draun Wulupner

The circuitry of this Row and Column bypassing multiplier is complex from other two bypassing techniques. In this, in each stage of CSA array AND gate and OR gate is used which increases the hardware complexity.

## VII. Synthesis and Simulation Result

The synthesis of Braun multiplier has been performed by using Xilinx ISE 14.4 tool & simulation has been done using Isim 14.4 simulation tool on Spartan 6 family, device Xc6slx45, package as csg324 with speed grade -3. The RTL schematic of 16 bit Braun multiplier with Row Bypassing using RCA and KSA is shown in below fig. 8, 9 and the simulation view of 16 bit Braun multiplier with Row Bypassing is shown in below fig 10.

Fig8. RTL Schematic of 16 Bit Row Bypassing Multiplier with RCA

Fig9. RTL Schematic of 16 Bit Row Bypassing Multiplier with KSA

| Name        |       | 270.000 ns            |                |        |  |  |

|-------------|-------|-----------------------|----------------|--------|--|--|

|             | Value | 250 ns                | [280 ns        | 300 ns |  |  |

| 🕨 🙀 pj310j  | 4624  | . ( 65792 ) ( 65792 ) | (4624 )(468 )( | 16 X 0 |  |  |

| 🕨 🗋 a(15:0) | 17    | 3 27 28               | 17 ( 16 )      | 1)(0)  |  |  |

| ▶ 👹 b(15:0) | 272   | 256 257               | <u>m (</u> m ) | 16 X 1 |  |  |

Fig10. Simulation result of 16 bit row bypassing multiplier with RCA and KSA

Fig13. Simulation Result of 16 Bit Column Bypassing Based Braun Multiplier with KSA

The RTL schematic of 16 bit Braun multiplier with Column bypassing using RCA and KSA is shown in below fig. 11, 12 and the simulation result of 16 bit Braun multiplier with Column bypassing using RCA and KSA is shown in below fig. 13.

Fig11. RTL Schematic of 16 Bit Column Bypassing Based Braun Multiplier with RCA

Fig12. RTL Schematic of 16 Bit Column Bypassing Based Braun Multiplier with KSA

The RTL schematic of 16 bit Braun multiplier with Row and Column (mixed) bypassing using RCA and KSA is shown in below fig. 14, 15 and the simulation view of 16 bit Braun multiplier with Row and Column (mixed) bypassing using RCA and KSA is shown in below fig. 16.

Fig14. RTL Schematic of 16 Bit Row and Column Bypassing Based Braun multiplier with RCA

Fig15. RTL Schematic of 16 Bit Row and Column Bypassing Based Braun multiplier with KSA

| Name        | Value    | 400 ms       | till ns | 420 rs        |

|-------------|----------|--------------|---------|---------------|

| 🕨 👹 p[31:0] | 19018257 | ) 19013888 ) | 4353    | 59888         |

| 🕨 🚺 aj150j  | 4369     | X 452 X      | 4653    | <b>X</b> 4368 |

| ▶ 👹 b[154]  | 4353     | )( 439 )(    | 1       | χ <u>15</u>   |

Fig16. Simulation result of 16 bit Row and Column bypassing based Braun multiplier with RCA and KSA.

| VIII. | Comparison Table for All Bypassing Technique |

|-------|----------------------------------------------|

|       | using RCA & KSA                              |

| Temp. Power Concumption (in Watt) |       |                             |                 |             |                 |  |

|-----------------------------------|-------|-----------------------------|-----------------|-------------|-----------------|--|

|                                   | remp. | Power Consumption (in Watt) |                 |             |                 |  |

| Bit Length                        |       |                             |                 |             |                 |  |

| Div Length                        |       | 10 <sup>0</sup>             | <b>a a</b> 0    | <b>7</b> 00 |                 |  |

|                                   | Addet |                             | 25 <sup>0</sup> | 50°         | 75 <sup>0</sup> |  |

|                                   |       |                             |                 |             |                 |  |

| 4 bit row                         | RCA   | 0.039                       | 0.058           | 0.090       | 0.156           |  |

|                                   |       |                             |                 |             |                 |  |

| Bypass                            | KSA   | 0.029                       | 0.057           | 0.075       | 0.138           |  |

|                                   | DGI   | 0.075                       | 0.005           | 0.114       | 0.10.6          |  |

| 8 bit row                         | RCA   | 0.075                       | 0.085           | 0.116       | 0.186           |  |

| Bypass                            | KSA   | 0.029                       | 0.039           | 0.069       | 0.137           |  |

| Dypass                            | ка    | 0.029                       | 0.039           | 0.009       | 0.157           |  |

| 16 bit row                        | RCA   | 0.087                       | 0.095           | 0.130       | 0.200           |  |

| 16 bit row                        | Ren   | 0.007                       | 0.075           | 0.150       | 0.200           |  |

| Bypass                            | KSA   | 0.080                       | 0.094           | 0.125       | 0.190           |  |

|                                   |       |                             |                 |             |                 |  |

| 4 bit column                      | RCA   | 0.035                       | 0.045           | 0.087       | 0.140           |  |

| D                                 |       |                             |                 |             |                 |  |

| Bypass                            | KSA   | 0.028                       | 0.055           | 0.068       | 0.135           |  |

|                                   | RCA   | 0.069                       | 0.059           | 0.110       | 0.127           |  |

| 8 bit column                      | KCA   | 0.009                       | 0.039           | 0.110       | 0.127           |  |

| Bypass                            | KSA   | 0.056                       | 0.045           | 0.110       | 0.115           |  |

|                                   |       |                             |                 |             |                 |  |

| 16 bitcolumn                      | RCA   | 0.085                       | 0.087           | 0.123       | 0.187           |  |

|                                   |       |                             |                 |             |                 |  |

| Bypass                            | KSA   | 0.075                       | 0.082           | 0.120       | 0.184           |  |

|                                   | DGL   | 0.020                       | 0.005           | 0.070       | 0.100           |  |

| 4 bit mixed                       | RCA   | 0.028                       | 0.037           | 0.062       | 0.133           |  |

| Bypass                            | KSA   | 0.026                       | 0.034           | 0.060       | 0.128           |  |

| 25 <b>P</b> ubb                   | ка    | 0.020                       | 0.054           | 0.000       | 0.128           |  |

| 0.14                              | RCA   | 0.045                       | 0.043           | 0.110       | 0.137           |  |

| 8 bit mixed                       | КСА   | 0.045                       | 0.045           | 0.110       | 0.157           |  |

| Bypass                            | KSA   | 0.029                       | 0.039           | 0.101       | 0.123           |  |

|                                   |       | 5.022                       | 0.007           | 0.101       | 0.120           |  |

| 16 bit mixed                      | RCA   | 0.080                       | 0.083           | 0.117       | 0.185           |  |

|                                   |       |                             |                 |             |                 |  |

| Bypass                            | KSA   | 0.073                       | 0.082           | 0.114       | 0.184           |  |

|                                   |       |                             |                 |             |                 |  |

## IX. Conclusion

4/8/16 bit Row Bypassing, Column Bypassing and mixed (Row and Column) bypassing is implemented using RCA and KSA in Xilinx ISE 14.4 tool and it is simulated by using ISIM 14.4 simulator and both are compared. From the above comparison table it is concluded that for 4/8/16 bit Row,

Column bypassing and mixed bypassing Braun multiplier less power is consumed using KSA when compared from RCA and hence speed can be improved. For 16 bit Row and Column Bypassing Technique using KSA the consumed power is found to 0.184 Watt. From other two methods (Row Bypass and Column Bypass) it is found to be 0.190 Watt and 0.184 Watt respectively

# X. Future Work

In this paper 4\*4, 8\*8 and 16\*16 bit multipliers are designed for unsigned bit multipliers. The bypassing techniques can also be applied to signed array multiplier architectures. It can also be implemented for the higher bit length like 32\*32 and 64\*64 bit in future. The design of multipliers considered here involved the use of RCA and KSA. The value of delay and power can also be reduced by using some other PPAs like BKA, SKA, LDA, and HCA etc.

## References

[1] Manchal Ahuja, Sakshi(2014) "Design of Bypassing multiplier with different Adders", Universal Journal of Electrical and Electronic Engineering.

[2] Teffi Francis, Tresa Joseph, Jobin K Antony (July 2013), "Modified mac unit for low power high speed dsp application using Multipler with bypassing technique and optimized adders".

[3] K. S. Ganesh Kumar, J. Deva Prasannam, M. Anitha Christy (March 2014), "Analysis of Low Power, Area and High Speed Multipliers for DSP applications", International Journal of Emerging Technology and Advanced Engineering (IJETAE).

[4] Sharvari S. Tantarpale, "Low-Cost Low-Power Improved Bypassing-Based Multiplier", International Journal of Computer Science and Communication Engineering (IJCSCE), ISSN 2319-7080, 2013.

[5] Abhishek Tundon, Ahmad (June 2013), "Design of Braun's multiplier using Han Carlson and Ladner Fischer Adders", International Journal of VLSI and Embedded Systems, (IJVES), ISSN: 2249 – 6556, Volume 4.

[6] Anitha ,Lincy Jesima (May-June 2012)., "Comparative Study of High performance Braun's Multiplier using FPGAs", IOSR Journal of Electronics and Communication Engineering (IOSRJECE) ISSN: 2278-2834 Volume 1, Issue 4.

[7] Ms. Madhu Thakur ,Prof. Javed Ashraf (October-2012, "Design of Braun Multiplier with Kogge Stone Adder & It's Implementation on FPGA", International Journal of Scientific & Engineering Research (IJSER), ISSN 2229-5518 Volume 3.

[8] J. Sudha Rani , D. Ramadevi, B. Santhosh Kumar, Jeevan Reddy K (Nov. - Dec. 2012)., "Design of Low Power Column bypass Multiplier using FPGA", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) ISSN: 2319 – 4200, Volume 1, Issue 3.

[9] Ming-ChenWen, Sying-Jyan Wang, and Yen-Nan Lin, "Low Power Parallel Multiplier with Column Bypassing", IEEE 2005.

[10] Rutesh S. Lonkar, Pravin P. Ashtankar, Nitin S. Ambatkar (2012), "Study Analysis of Various Low Power Zero Partial Product Bypass Multipliers", International Journal of Electronics Communication and Computer Engineering (IJECCE), Volume 3, Issue 2, ISSN 2249–071X.

[11] Yin-Tsung Hwang, Jin-Fa Lin, Ming-Hwa Sheu and Chia-Jen Sheu (2007), "Low Power Multipliers using enhenced row bypassing schemes", IEEE.

[12] Soniya, Suresh Kumar (July – August 2013), "A Review of Different Type of Multipliers and Multiplier-Accumulator Unit",

International Journal of Emerging Trends & Technology in Computer Science (IJETTCS), ISSN 2278-6856, Volume 2, Issue 4. [13] Mohammed Hasmat Ali, Anil Kumar Sahani (June 2013), "Study, Implementation and Comparison of Different Multipliers based on Array, KCM and Vedic Mathematics using EDA Tools", International Journal of Scientific and Research Publications (IJSRP), ISSN 2250-3153, Volume 3, Issue 6.

[14] Savita Nair, Ajit Saraf (2014), "A Review Paper on Comparison of Multipliers based on Performance Parameters", International Conference on Advances in Science and Technology (ICAST).

[15] M.Jayaprakash, M.Peer Mohamed, Dr.A.Shanmugam (January 2014), "Design and Analysis of Low Power and Area Efficient Multiplier", International Journal of Electrical, Electronic and Mechanical Controls, ISSN: 2319-7501, Volume 3 Issue 1.