# Preview paper on digital comparator for better Noise Response and Higher Speed

1Deepika Soni, 2Karishma Sahu

1Asst.Professor, 2Student M.Tech, Gyan Ganga Institute of Technology and Science, Jabalpur

Abstract: This paper introduces a survey on advanced comparator for better commotion reaction and higher speed. It depends on the general type of the n-bit computerized comparators with lion's share capacities. Different paper has been examined for finding the best procedure for change of clamor proportion and speed for quicker operation of comparator The requirement for low power, range productive and rapid comparator is pushing towards the utilization of timed computerized comparator which augment speed and power proficiency. As CMOS innovation downsizes, different short channel impacts emerges which builds the spillage current because of low limit voltage and waste some rate of force as spillage power Conversion amongst simple and advanced signs is a fundamental capacity in flag preparing. With the most recent advances in flag handling, the requirement for quick and low-control simple to computerized and computerized to-simple converters is expanding. In A/D converters, comparators have high impact on the accomplished execution

*Index Terms*— Digital Comparator, Differential Amplifier, Speed, Noise.

#### I. Presentation

Comparators are most broadly utilized electronic parts after operational intensifiers in this world. The essential usefulness of a CMOS comparator is utilized to discover regardless of whether a flag is more noteworthy or littler than zero or to analyze an info motion with a reference flag and yields a double flag in view of correlation .This Paper survey all the advanced comparator as indicated by their plan and propose best out of those which has better Noise Response and Higher Speed. Whatever is left of the paper is sorted out as takes after: The system in area II comprise of many outlines from distinctive paper and, FINALLY, conclusion in area III.

#### II. System

## A. Half and half Digital Comparator

The half and half comparator technique, parallel sidestep COD (PBCOD) is composed with the expectation of accomplishing critical change in deferral and power. The PBCOD outline shown in Fig.1, acknowledges two data sources An and B each of N bit width and produces three yield signals, showing their imbalance. The info operands An and B are at first encoded utilizing BCL pre-encoder [6] to dispose of all "equivalent to" cases. The choice square considers N.R most huge bits from each encoded operand as its data sources and produces the determination Signals, A\_EN and S\_EN. The proportion parameter (R) chose by the fashioner decides the quantity of COD and parallel Submodules.

Facilitate, the estimation of R is limited between the cutoff points of 0 to 0.5 while N.R is a various of 4 and more prominent than 4.

Figure 1. PBCOD square chart

The parallel and COD comparator (CMP) modules involve of 4-bit sub-modules each. In view of N.R, the quantity of COD what's more, parallel sub-modules are chosen. The aggregate number of sub-modules in any PBCOD framework is N/4, which is settled for any given estimation of N.

The pre-encoding guarantees that A\_EN might be set when either An or B is more noteworthy in first N.R bits. At the point when the control flag A\_EN is actuated, the COD unit is chosen and examination advances serially through the primary N.R most noteworthy bits. Then again, if S\_EN flag is empowered, the parallel piece is chosen and N. (1 - R) bits are looked at. For example, if N = 8 and R = 0.5, PBCOD plot comprises of one COD sub-module and one parallel sub modules and the comparing choice guarantees that choice signs A\_EN what's more, S\_EN are fundamentally unrelated and the last yield rationale is acquired by means of mux based choice rationale.

A point by point well ordered strategy of PBCOD configuration is introduced in Algorithm.1. The two paired N-bit numbers, A also, B are encoded utilizing the BCL pre-encoder at first. These encoded numbers, An' and B' are utilized to create the determination signals

(A\_EN and S\_EN). The documentation " is utilized to indicate the encoding operation. In light of the control flag, the chose framework plays out the last correlation.

#### B. Low power decrease system

In this segment we explored some low power strategies in detail with some issue related with them also, connected on timed computerized comparator which is the base instance of examination.

a. Control Gating Approach

In power gating(PG) approach the PMOS transistor which is getting contribution from rest isolating the Vdd from draw up system and NMOS transistor getting contribution from Sleep' isolating the draw down system from ground [7]-[8]. The edge estimation of rest transistor is high as contrast with pullup what's more, draw down system transistor, so in remain by mode spillage current is low. The W/L proportion of rest transistor is shifted with the goal that limit esteem is higher than principle circuit.Transistor measuring, information maintenance and deferral are primary issues with this approach however control utilization and spillage current is lessened which is the favorable position. Different investigation is conveyed out with various CMOS innovation at 1.2V supply voltages for CDC-control gating. The fig. (2) Showing the schematic of timed advanced comparator with power gating approach.

Fig. 2. Timed advanced comparator with Power Gating.

## b. Crisscross Approach

In Zigzag (ZZ) approach rest transistor are associated in crisscross mold i.e. some rest transistors are associated with Pull-up system of circuit and some are associated with draw down system of circuit in crisscross way as appeared in fig.(3) [8]. The primary issue with this approach is that yields brings about obliteration of states and deferral is additionally high. The schematic of CDC-Zigzag is appeared in fig. (3), likewise different investigation is completed to improve understanding about this topology

Fig. 3. Timed computerized comparator with Zigzag approach.

# c . Spillage Feedback approach

spillage criticism approach(LFA) is the augmentation of force gating approach which evacuates the issue of information maintenance, yet, we need to relinquish for power which is higher than power gating approach likewise region prerequisite is expanded [8]-[9]. In this approach one assistant NMOS in parallel to NMOS rest transistor and PMOS in parallel to PMOS rest transistor are associated and they are getting contribution from the yield of additional inverter as appeared in fig.(4). Timed advanced comparator with spillage input approach is explored and different examination is completed.

Fig. 4. Timed advanced comparator with Leakage Feedback approach.

Fig. 5. Timed advanced comparator with Dual Stack approach.

## d. Double Stack Approach

In double stack approach(DS) two PMOS and two NMOS transistors are associated in parallel course of action as appeared in given fig.(5) [8] - [10]-[11]. The no. of transistor check is bigger than past plan approach which prompt to bigger region, likewise postponement is punishment. Be that as it may, this approach lessens the spillage power and normal power utilization. Different investigation is done to assess control, spillage current, delay, control postpone item (PDP) and range at various innovation.

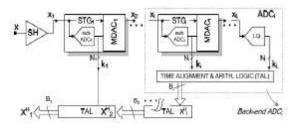

# C. Comparator OFFSET Effects In Pipeline ADCS

Fig. 6 demonstrates a disentangled piece graph of a (L-1)arrange Pipeline ADC, with a last quantise (LQ). Every stage, STGi With i ɛ [1, L-1], contains: an) a subADCi which digitalizes its simple information xi giving and the subcode ki with Ni-bit determination; and b) a MDACi which produces the enhanced deposit xi+1 to be prepared by the accompanying stages. The computerized representation X1 H of the converter input  $x \approx x1$  is at last got, by the TAL (Time Alignment and Arithmetic Logic), as a straightforward parallel weighted capacity of the synchronized codes  $\{ki\}$  with i = 1, ..., L. Due to the recursive nature of the Pipeline design, the back-end stages from STGi to LQ shape a simple to-advanced converter, marked ADCi in Fig. 1, the yield code of which is an advanced estimation Xi H = ADCi(xi).The subADCi design is traditionally in light of a Flash ADC made up of a bank of M comparators, a resistor stepping stool for the move voltage era, tj, and a thermometer-to-parallel encoder which classifies the simple input flag x  $\varepsilon$  [-R,R], into the N-bit yield code, k  $\varepsilon$  [0,M]. The relationship between x, the arrangement of moves {tj}, the yield code k and the comparator counterbalance are given by,

Fig. 6. Improved piece outline of a L-organize Pipeline ADC with subtle elements of stage topology and time arrangement and number juggling rationale (TAL).

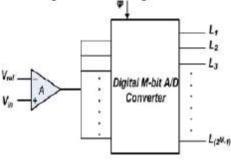

D. High-Resolution Semi-Digital Comparator Engineering

Keeping in mind the end goal to have discretionary examination levels and to empower high determination A/D converters utilizing the computerized comparator, a semi-computerized comparator structure is proposed. Fig. 7 appears the square chart of the semi-computerized multi-level comparator.

Fig.7. High-Resolution Semi-Digital multi-level Comparator square chart

The proposed comparator comprises of a differential speaker of pick up A fell with a computerized M-bit A/D converter. The differential preamplifier stage is utilized to enhance the distinction what's more, apply the outcome to the fell computerized A/D converter such that the required LSB is gotten, where Expanding the pick up An accomplishes higher determination while ensuring monotonicity of the utilized levels. All-computerized A/D converter examination levels' variety because of process impacts constitutes a settled proportion of the LSBsemicomputerized Where LSBdigital-ADC speaks to the procedure variety impacts on the LSBdigital-ADC. The intensifier pick up variety because of predisposition and prepare impacts likewise constitutes a settled proportion of the LSBsemi-advanced where  $\Delta A$  speaks to the variety in the speaker pick up. The crisscross of the info differential combine in the preamplifier organize, the variety of the preamplifier yield DC level, the allcomputerized A/D converter examination levels' variety  $\Delta$ LSBdigital-ADC, and the supply voltage VDD variety cause an input alluded balance that are settled for all the correlation levels what's more, henceforth monotonicity is ensured. With a specific end goal to accomplish high precision utilizing the semi-advanced comparator, a counterbalance cancelation circuit might be utilized to take out the created balanced. Luckily, just a single counterbalance cancelation circuit is required for each of the 2M semi-computerized comparator's levels, where M is the determination of the utilized advanced A/D converter. Furthermore, the semi-advanced comparator needs one information reference voltage Vref for every one of the 2M correlation levels. Then again, in old comparator topologies [12], [13], every correlation level needs a speaker, a counterbalance cancelation circuit, and an information reference. Subsequently, a critical power and zone decrease of glimmer A/D converters that is built through the proposed semi-advanced comparator can be accomplished. For sure, a streak A/D converter, constructed utilizing semi-advanced comparators, has a lessening in the required power and zone by around a element of 2M when contrasted with a built blaze A/D converter utilizing the old comparator topologies.

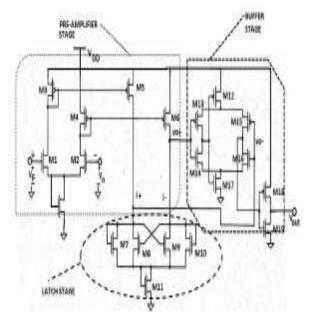

# E. Preamplifier based comparator

There are different sorts of comparator designs accessible in our today's electronic world. Among these comparators, we broke down the static and element attributes and focal points also, inconveniences of Preamplifier Based Comparator i.e. comparators having a preamplifier taken after by a regenerative lock organize which is again trailed by a yield cushion (which is fundamentally a self-one-sided differential speaker) and Fully Dynamic Latched Comparators i.e. Comparators having positive input based consecutive hook arrange that decides yield of the circuit Circuit above demonstrates the preamplifier based comparator. The comparator comprises of three phases: the info preamplifier organize, a hook arrange, and a yield cradle arrange (it is fundamentally a self-one-sided differential intensifier took after by an inverter which gives the computerized yield. The preamplifier stage is fundamentally a differential speaker with dynamic burdens. The preamp stage (or stages) increases the info flag to move forward the comparator affectability (i.e., expands the base information motion with which the comparator can settle on a choice) and detaches the contribution of the comparator from exchanging commotion (frequently called kickback commotion) originating from the positive input arrange. It likewise can decrease enter alluded lock counterbalance voltage. The sizes of Ml and M2 are set by considering the diff-amp trans-conductance and the info capacitance

#### F. Double-Tail Dual-Rail Dynamic Latched Comparator

Figure 8: Preamplifier based comparator.

Figure 9: Double-Tail Dual-Rail Dynamic Comparator

This comparator dispensed with the debilitated Ni hubs by embeddings an inverter amongst info and yield stages. Due to inverter, powerless flag of Ni hub is recovered and nourished to the yield organize. This comparator demonstrates quicker operation and lesser power dissemination than the past comparators.

### **III. CONCLUSION**

In this proposed paper, Various paper has been examined for finding the best system for development of clamor proportion and speed for quicker operation of comparator The requirement for low control, range proficient and rapid comparator is pushing towards the utilization of timed computerized comparator which amplify speed and power proficiency. Thus for advanced comparator plan for better commotion reaction and higher speed consecutive inverter is supplanted with double info single yield differential intensifier in the hooked stage. The clamor display in the information stage and clock can be smothered by differential intensifier display in yield arrange.

## REFERENCES

[1] Syed Ershad Ahmed, Sweekruth Srinivas S, M.B.Srinivas "An Energy Proficient Hybrid Digital Comparator" 29th International Conference on VLSI Design and 2016 fifteenth International Conference on Embedded Frameworks IEEE 2016 ISSN

[2] Sameer Thakre ,Pankaj Srivastava," Design and Analysis of Low-Power Fast Clocked Digital Comparator" Global Conference on Correspondence Technologies IEEE 2015 ISSN 978-1-4799-8553-1

[3] A. J. Ginés, E. Peralías, C. Aledo, A. Rueda "Control Optimization and Organize Op-amp Linearity Relaxation in Pipeline ADCs with Digital Comparator Offset Calibration"IEEE pilgrim 2014 ISSN 978-1-4799- 5743-9

[4] Loai Salem and Yehea Ismail "All-Digital Comparator Using Device- Proportion programmable Triggering Levels"IEEE pilgrim 2011

[5] Mohammad Larijani, and Mohammad bagher Ghaznavi-Ghoushchi," A 4.2GHz, 3.3mW, 1.1pJ, 90nm 64-bit New Digital Comparator with 1.2 Clock Pipeline Delay",

[6] J.- Y. Kim and H.- J. Yoo, "Bitwise rivalry rationale for reduced computerized comparator," in Solid-State Circuits Conference, 2007.

[7] Chun, Jae Woong, and CY Roger Chen, "A novel spillage control decrease strategy for CMOS circuit plan," In International SoC Plan Conference (ISOCC), pp. 119-122. IEEE , 2010.

[8] Lorenzo, Rohit, and Saurabh Chaudhury, "another ultra low spillage and rapid system for CMOS circuits," In Students Conference on Designing and Systems (SCES), pp. 1-5. IEEE, 2014.

[9] Pal, Pankaj Kr, Rituraj S. Rathore, Ashwani K. Rana, and GauravSaini, "amazing failure control systems: Leakage Feedback with Stack and Rest Stack with Keeper," In International Conference on Computer and Correspondence Technology (ICCCT), pp. 296-301. IEEE, 2010.

[10] Chowdhury, Asif Jahangir, Md Shahriar Rizwan, Shahriar Jalal Nibirwhat's more, Md Rifat Alam Siddique, "A New Leakage diminishment Method for ultra Low Power VLSI Design for versatile gadgets," In second Worldwide Conference on Power, Control and Embedded Systems (ICPCES), pp. 1-4. IEEE, 2012.

[11] Islam, M. S., M. Sultana Nasrin, Nuzhat Mansur, and Naila Tasneem, "Double stack strategy: A novel way to deal with low

spillage and speed control item VLSI plan," International Conference on Electrical and PC Engineering (ICECE), pp. 89-92. IEEE, 2010.

[12] B. Razavi and B. A. Wooley, "Outline Techniques for High-speed, High-Resolution Comparators," IEEE J. Strong State Circuits, Vol. 27, No. 12, pp. 1916-1926, DEC. 1992., in press.

[13] G. M. Yin, F. O. Eynde, and W. Sansen, "A High-Speed CMOS Comparator with 8-b Resolution," IEEE J. Strong State Circuits, Vol. 27, No. 2, pp. 208-211, Feb. 1992., in

[14] Jun He, Sanyi Zhan, Degang Chen, and R.L. Geiger, "Investigations of Static and Dynamic Random Offset Voltages in Dynamic Comparators," IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 56, pp. 911-919, May 2009.

[15] T. Kobayashi, K. Nogami, T. Shirotori and Y. Fujimoto, "A currentcontrolled lock sense speaker and a static powersparing information cradle for low-control engineering," IEEE J. Strong State Circuits, vol. 28, pp. 523-52, April 1993.

[16] B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and speed streamlining of a hook sort voltage sense intensifier", IEEE J. Strong State Circuits, vol. 39, pp. 1148-1158, July 2004.

[17] D. Schinkel, E. Mensink, E. Kiumperink, E. van Tuijl and B. Nauta, "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time," ISSCC Dig. Tech. Papers, pp. 314-315 and 605, Feb. 2007.

[18] M. Miyahara, Y. Asada, P. Daehwa and A. Matsuzawa, "A Low- Clamor Self-Calibrating Dynamic Comparator for High-Speed ADCs," in Proc. A-SSCC, pp. 269-272, Nov. 2008.

[19] H.J. Jeon, Y.B. Kim, "A Low-counterbalance High-speed Double-tail Dual-rail Dynamic Latched Comparator," ACM GLSVLSI'10(Great Lakes Symposium on VLSI), May 16-18, 2010.

[20] Jun He, Sanyi Zhan, Degang Chen, and R.L. Geiger, "Examinations of Static and Dynamic Random Offset Voltages in Dynamic Comparators," IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 56, pp. 911-919, May 2009.

[21] Syed Ershad Ahmed, Sweekruth Srinivas S, M.B.Srinivas "An Energy Effective Hybrid Digital Comparator" 29th International Conference on VLSI Design and 2016 fifteenth International Conference on Embedded Frameworks IEEE 2016 ISSN