# Survey Paper on Radix DIT & DIF Fast Fourier Transforms using Complex Input

<sup>1</sup>Neetu Gautam, <sup>2</sup>Prof Bharti Chourasia <sup>1</sup>M Tech. Scholar, <sup>2</sup>Head of Dept. Dept. of Electronics and Communication SCOPE College of Engineering, Bhopal

neetugautambe09@gmail.com

*Abstract*— The Fast Fourier change (FFT) is an as often as possible utilized Digital sign preparing (DSP) calculations for the uses of Orthogonal Frequency Division multiplexing (OFDM). The blend of Orthogonal Frequency Division Multiplexing (OFDM) with Multiple Input Multiple Output (MIMO) signal handling is a clear approach of upgrading the information rates of different correspondence frameworks, for example, Wireless LAN, e Mobile, 4G and so on. Since FFT processor is an intricate module in OFDM, it is exceedingly unavoidable to plan the processor in a productive way. This research work involved the implementation of a low delay and area efficient radix-2, radix-3 and radix-4 decimation in time (DIT) using 8-point, 16-point, 32point, 64-point, 128-point, 256-point and 512-point algorithm using radix-2 butterfly. In this paper is used unsigned, signed and complex number for radix-2 algorithm.

*Index Terms*— FFT, Decimation in Time, Decimation in Frequency, real Value data

## I. INTRODUCTION

Computerized signal preparing (DSP) is the scientific control of a data sign to adjust or enhance it somehow. It is portrayed by the representation of discrete time, discrete recurrence, or other discrete area signals by a succession of numbers or images and the preparing of these signs [1].

The objective of DSP is for the most part to quantify, channel and/or pack nonstop genuine simple signs. The initial step is for the most part to change over the sign from a simple to an advanced structure, by inspecting and after that digitizing it utilizing a simple to-computerized converter (ADC), which transforms the simple sign into a surge of numbers. Be that as it may, regularly, the required yield sign is another simple yield signal, which requires an advanced to-simple converter (DAC). Regardless of the fact that this procedure is more mind boggling than simple preparing and has a discrete worth range, the use of computational energy to advanced sign handling considers numerous points of interest over simple handling in numerous applications, for example, mistake recognition and revision in transmission and additionally information pressure. DSP calculations have for quite some time been keep running on standard PCs, and in addition on particular processors called advanced sign processor and deliberately assembled equipment, for example, applicationparticular coordinated circuit (ASICs). Today there are extra advances utilized for computerized signal preparing including

all the more intense broadly useful chip, field-programmable door exhibits (FPGAs), advanced sign controllers (generally for mechanical applications, for example, engine control), and stream processors, among others [2-3]. The FFT is a standout amongst the most normally utilized advanced sign preparing calculation. As of late, FFT processor has been generally utilized as a part of advanced sign handling field connected for OFDM, MIMO-OFDM correspondence frameworks. FFT/IFFT processors are key segments for an orthogonal recurrence division multiplexing (OFDM) based remote IEEE 802.16 broadband correspondence framework; it is a standout amongst the most unpredictable and concentrated calculation module of different remote guidelines physical layer (ofdm-802.11a, MIMO-OFDM 802.11, 802.16,802.16e) [4].

Some collapsed pipeline models have been proposed for the calculation of RFFT [3], [4], where butterfly operations are multiplexed into a little rationale unit. The structures in [3] and [4] could give satisfactory throughput to a few applications yet the capacity multifaceted nature of those structures keeps on being high. A couple set up structures has additionally been proposed for RFFT utilizing particular pressing calculations [5], [6]. Memory-struggle for read/compose operation is observed to be the significant test in the outline of calculations and structures for set up calculation [7]. As of late, a set up engineering and strife free memory tending to conspire have been proposed for persistent preparing of RFFT [8].

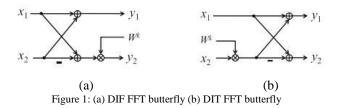

The FFT calculations are arranged into two general classes, to be specific, the demolition in-time (DIT) and the destruction uncommonness (DIF) calculations. The key contrasts between the two are appeared in Fig. 1. If there should arise an occurrence of DIF calculation (Fig. 1(a)), the info tests are bolstered to the registering structure in their regular request, while the yield is created in bit-switched request. Then again, if there should be an occurrence of DIT calculation (Fig. 1(b)), the info tests need bit-inversion reordering before being handled, while the yield FFT coefficients are created in characteristic request. In various RFFT applications, for example, picture and video handling, biomedical sign preparing, and time-arrangement investigation and so forth., the complete info grouping is for the most part accessible together in the meantime for the FFT calculation. The DIT RFFT has an advantage over the DIF form for these applications, since a DIT RFFT structure need not wait for the

arrival of input samples but can produce the outputs as soon as those are computed.

#### **II. LITERATURE REVIEW**

Pramod Kumar Meher et al. [7], the demolition in-time (DIT) quick Fourier change (FFT) regularly has advantage over the obliteration in-recurrence (DIF) FFT for most genuine esteemed applications, similar to discourse/picture/video handling, biomedical sign preparing, and time-arrangement investigation, and so forth., since it doesn't require any yield reordering. Furthermore, the DIT FFT butterfly includes less calculation time than its DIF partner. In this paper, we exhibit an effective engineering for the radix-2 DIT genuine esteemed FFT (RFFT). We exhibit here the essential numerical detailing for expelling the redundancies in the radix-2 DIT RFFT, and present a definition to regularize its stream chart to encourage collapsed calculation with a straightforward control unit. We propose here a register-based capacity outline which includes essentially less zone at the expense of somewhat higher inertness contrasted and the traditional RAM-based capacity. The location era for collapsed set up DIT RFFT calculation with register-based capacity is trying following both read and compose operations are performed in the same clock cycle at various areas. Along these lines, we show here a straightforward definition of location era for the proposed radix-2

DIT RFFT structure. The proposed structure includes 61% less territory and 40% less power utilization than those of [8], all things considered, for FFT sizes 16, 32, 64, and 128. It includes 70% less zone delay item and 57% less vitality for every specimen than those of the other, all things considered, for the same FFT sizes.

Manohar Ayinala et al. [8], this brief introduces a novel versatile engineering for set up quick Fourier change (IFFT) calculation for genuine esteemed signs. The proposed calculation depends on a changed radix-2 calculation, which expels the excess operations from the stream chart. Another handling component (PE) is proposed utilizing two radix-2 butterflies that can procedure four inputs in parallel. A novel clash free memory-tending to plan is proposed to guarantee the ceaseless operation of the FFT processor. Besides, the tending to plan is stretched out to bolster numerous parallel PEs. The proposed genuine FFT processor at the same time requires less calculation cycles and lower equipment cost contrasted with earlier work. For instance, the proposed outline with two PEs decreases the calculation cycles by a component of 2 for a 256-point genuine quick Fourier change (RFFT) contrasted with an earlier work while keeping up a lower equipment unpredictability. The quantity of calculation cycles is decreased proportionately with the expansion in the quantity of PEs.

Shashank Mittal et al. [9], quick Fourier Transform (FFT) is a standout amongst the most fundamental and vital operation performed in Software Defined Radio (SDR). Consequently outlining a widespread, reconfigurable FFT calculation obstruct with low range, postpone and control necessity is critical. As of late it is demonstrated that Bruun's FFT is in a perfect world suited for SDR notwithstanding when working with higher piece exactness to keep up same NSR. In this paper, creators have proposed another engineering for Bruun's FFT utilizing an appropriated approach for increasing the quantity of bits (exactness) with progressive phases of FFT. It is likewise demonstrated that proposed engineering further lessens the equipment prerequisite of Bruun's FFT with immaterial changes in its NSR. The proposed outline makes Bruun's FFT, a superior choice for most useful cases in SDR. A point by point correlation of Bruun's customary and proposed equipment structures for same NSR is completed and consequences of FPGA and ASIC usage are given and talked about.

Byung G. Jo et al. [10], the paper proposes a new continuousflow mixed-radix (CFMR) fast Fourier transform (FFT) processor that uses the MR (radix-4/2) algorithm and a novel in-place strategy. The existing in-place strategy supports only a fixed-radix FFT algorithm. In contrast, the proposed in-place strategy can support the MR algorithm, which allows CF FFT computations regardless of the length of FFT. The novel inplace strategy is made by interchanging storage locations of butterfly outputs. The CFMR FFT processor provides the MR algorithm, the in-place strategy, and the CF FFT computations at the same time. The CFMR FFT processor requires only two -word memories due to the proposed in-place strategy. In addition, it uses one butterfly unit that can perform either one radix-4 butterfly or two radix-2 butterflies. The CFMR FFT processor using the 0.18 m SEC cell library consists of 37,000 gates excluding memories, requires only 640 clock cycles for a 512-point FFT and runs at 100 MHz. Therefore, the CFMR FFT processor can reduce hardware complexity and computation cycles compared with existing FFT processors.

Table 1: Comparison of the FFT architecture considering latency and area

| Reference | Multiplier | Adder | MUX/ | Computation            |

|-----------|------------|-------|------|------------------------|

|           |            |       | DMUX | Time                   |

| [10]      | 12         | 22    | 38   | N/4 log <sub>4</sub> N |

| [9]       | 9          | 19    | 38   | N/4 log <sub>2</sub> N |

| [8]       | 4          | 6     | 38   | N/4 log <sub>2</sub> N |

| [7]       | 4          | 6     | N+12 | N/4 log <sub>2</sub> N |

#### **III. FFT ALGORITHM**

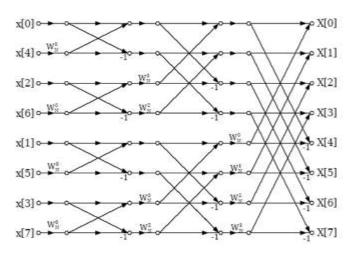

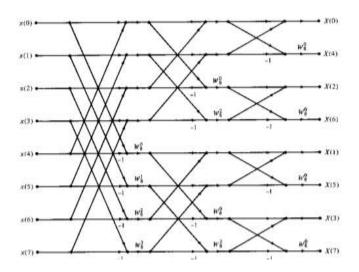

A fast Fourier transform (FFT) is an algorithm to compute the discrete Fourier transform (DFT) and its inverse. Fourier analysis converts time (or space) to frequency and vice versa; an FFT rapidly computes such transformations by factorizing the DFT matrix into a product of sparse (mostly zero) factors. As a result, fast Fourier transforms are widely used for many applications in engineering, science, and mathematics. Show the butterfly operations for radix-2 DIF FFT in figure 2 and figure 3. The radix-2 algorithms are the simplest FFT butterfly algorithm.

Figure 2: Radix-2 Decimation in Time Domain FFT Algorithm

Figure 3: Radix-2 Decimation in Frequency Domain FFT Algorithm

# **IV. METHODOLOGY**

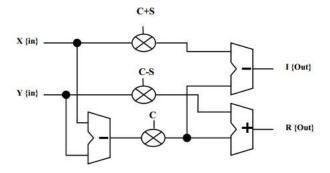

Since complex multiplication is an expensive operation, we tend to reduce the multiplicative complexity of the twiddle factor inside the butterfly processor by calculating only three real multiplications and three add/subtract operations as in the twiddle factor multiplication:

$$R + jI = (X + jY).(C + jS)$$

(1)

However the complex multiplication can be simplified:

$$\mathbf{R} = (\mathbf{C} - \mathbf{S}) \cdot \mathbf{Y} + \mathbf{Z} \tag{2}$$

$$I = (C + S) . X - Z$$

(3)

With:

$$Z = C. (X - Y)$$

(4)

C and S are pre-computed and stored in a memory table. Therefore it is necessary to store the following three coefficients C, C + S, and C - S. The implemented algorithm of complex multiplication used in this work uses three multiplications, one addition and two subtractions as shown in Fig. 4.

5

Figure 4: Implementation of complex multiplication

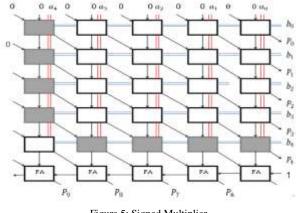

## Signed Multiplier:-

Baugh-Wooley algorithm for the signed binary multiplication is based on the concept shown in figure 5. The algorithm specifies that all possible AND terms are created first, and then sent through an array of half-adders and full-adders with the Carry-outs chained to the next most significant bit at each level of addition. Negative operands may be multiplied using a Baugh-Wooley multiplier.

Figure 5: Signed Multiplier

# V. CONCLUSION

The prime objective is to construct a FFT in order to have low power consumption and lesser area. The parameters (i) power consumption (ii) Area occupancy were given due consideration for comparing the proposed circuit with other FFTs. The circuits were simulated using Model-Sim 6.3c and synthesized with Xilinx ISE 14.1.The performance of various 64 point FFT such as Radix-2, Radix-4, split Radix, mixed -radix 4-2, R2MDC and the proposed modified R2MDC were carried out and their performance were analyzed with respect to the number of CLB slices, utilization factor and Power consumption.

## REFERENCES

- [1] Pramod Kumar Mehe, Basant Kumar Mohanty, Sujit Kumar Patel, Soumya Ganguly, and Thambipillai Srikanthan, "Efficient VLSI Architecture for Decimation-in-Time Fast Fourier Transform of Real-Valued Data", IEEE Transactions on Circuits And Systems—I: Regular Papers, Vol. 62, No. 12, December 2015.

- [2] Himanshu Thapaliyal and M.B Srinivas, "VLSI Implementation of RSA Encryption System Using Ancient Indian Vedic Mathematics", Center for VLSI and Embedded System Technologies, International Institute of Information Technology Hyderabad, India 2014.

- [3] M. Ayinala, Y. Lao, and K. K. Parhi, "An in-place FFT architecture for real-valued signals," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 60, no. 10, pp. 652–656, Oct. 2013.

- [4] S. S. Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A, "Implementation of Vedic multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011, Proceedings published by International Joural of Computer Applications® (IJCA), pp.1-6.

- [5] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics: Sixteen simple Mathematical Formulae from the Veda", Delhi (2011).

- [6] D. Tsonev, S. Sinanovic and H. Haas, "Enhanced subcarrier index modulation (SIM) OFDM," in IEEE Global Communications Conference (IEEE GLOBECOM 2011), 5–9Dec. 2011.

- [7] Charles. Roth Jr., "Digital Systems Design using VHDL", Thomson Brooks/Cole, 7th reprint, 2005.

- [8] S. S. Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A, "Implementation of Vedic multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011, Proceedings published by International Joural of Computer Applications® (IJCA), pp.1-6.

- [9] Himanshu Thapaliyal and M.B Srinivas, "VLSI Implementation of RSA Encryption System Using Ancient Indian Vedic Mathematics", Center for VLSI and Embedded System Technologies, International Institute of Information Technology Hyderabad, India.

- [10] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics: Sixteen simple Mathematical Formulae from the Veda", Delhi (2011).

- [11] Harpreet Singh Dhillon and Abhijit Mitra, "A Reduced-bit Multiplication Algorithm for Digital Arithmetic", International Journal of Computational and Mathematical Sciences, Febrauary 2008, pp.64-69.

- [12] Sumit Vaidya and Depak Dandekar. "Delay-power performance comparison of multipliers in VLSI circuit design". International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010.

- [13] Pramod Kumar Mehe, Basant Kumar Mohanty, Sujit Kumar Patel, Soumya Ganguly, and Thambipillai Srikanthan, "Efficient VLSI Architecture for Decimationin-Time Fast Fourier Transform of Real-Valued Data", IEEE Transactions on Circuits And Systems—I: Regular Papers, Vol. 62, No. 12, December 2015.

- [14] M. Ayinala, Y. Lao, and K. K. Parhi, "An in-place FFT architecture for real-valued signals," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 60, no. 10, pp. 652–656, Oct. 2013.

- [15] Shashank Mittal, Md. Zafar Ali Khan and M.B. Srinivas, "Area Efficient High Speed Architecture of Bruun's FFT for Software Defined Radio", 1930-529X/07/\$25.00 © 2007 IEEE.

- B. G. Jo and M. H. Sunwoo, "New continuous-flow mixed-radix (CFMR) FFT processor using novel in-place strategy," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 52, no. 5, pp. 911–919, May 2005.